## Scalable compact modeling of trap generation near the EB spacer oxide interface in SiGe HBTs

Marine Couret, Mathieu Jaoul, François Marc, Chhandak Mukherjee, Didier

Celi, Thomas Zimmer, Cristell Maneux

### ▶ To cite this version:

Marine Couret, Mathieu Jaoul, François Marc, Chhandak Mukherjee, Didier Celi, et al.. Scalable compact modeling of trap generation near the EB spacer oxide interface in SiGe HBTs. Solid-State Electronics, 2020, pp.107819. 10.1016/j.sse.2020.107819. hal-02541991

## HAL Id: hal-02541991 https://hal.science/hal-02541991

Submitted on 14 Apr 2020  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Scalable compact modeling of trap generation near the EB spacer oxide interface in SiGe HBTs

Marine Couret<sup>a</sup>, Mathieu Jaoul<sup>a,b</sup>, François Marc<sup>a</sup>, Chhandak Mukherjee<sup>a</sup>, Didier Céli<sup>b</sup>, Thomas Zimmer<sup>a</sup>, Cristell Maneux<sup>a</sup>

<sup>a</sup>IMS Laboratory, University of Bordeaux, UMS CNRS 5218, Cours de la Libération, 33405 Talence, France <sup>b</sup>STMicroelectronics, 38926 Crolles, France

#### Abstract

This paper presents a physics-based scalable formulation for interface trap generation in the vicinity of the emitterbase spacer oxide interface in advanced SiGe HBTs. Aging tests were performed for various emitter dimensions to investigate the scalability of the dynamics of hot-carrier degradation. An improved formulation of the bond dissociation rate is also proposed incorporating a scaling rule depending on the avalanche current density. The hydrogen diffusion through the EB spacer has been modeled using an RC ladder network and has been scaled according to the hydrogen diffusion volume. Its accuracy has been validated over a wide range of aging tests and various geometry features.

Keywords: SiGe HBTs, reliability, compact model, hot-carrier degradation, hydrogen diffusion

<sup>\*</sup>Corresponding author : marine.couret@u-bordeaux.fr

#### 1. Introduction

Due to the drastic miniaturization of electronic devices [1], electrical performances of advanced SiGe heterojunction bipolar transistors (HBTs) are constrained in terms of safe-operating-area (SOA). Over the last decades, the collector-emitter breakdown voltage ( $BV_{CEO}$ ) has decreased significantly to meet the demand of continuously increasing cut-off frequencies, thus limiting the available output power. Therefore, modern circuits are being forced to operate at higher voltages where hot-carrier degradation (HCD) mechanism is predominant. This degradation mechanism is now well known in SiGe HBTs where the hot-carriers created by impact ionization can reach the emitter-base (EB) spacer oxide interface, leading to the dissociation of the passivated Si-H bonds [2, 3, 4, 5]. The main electrical issue induced by HCD is the increase of the base current at low and moderate injection levels which thereby causes a large decrease of the current gain  $\beta$  as well as a degradation of the low-frequency noise [2].

Since HCD is a consequence of the impact ionization mechanism [6], the resulting avalanche current has to be accurately predicted at low and high current densities. A formulation for the avalanche multiplication factor has recently been proposed in [7] for extending the validation range of the avalanche multiplication factor up to high current densities. Thus, the extraction flow of the aging compact model parameters must start with an accurate extraction of the associated new avalanche parameters.

As pointed out in [8], some of the degradation attributes, such as the saturation value of the aging-induced shift in the base current or the degradation dynamics, are SiGe HBT architecture-dependent. Indeed, as demonstrated for the universality of HCD in MOSFET architectures [9], the degradation magnitude for SiGe HBTs will widely depend on the emitter dimensions [10], the Si/SiO<sub>2</sub> interface quality as well as the spacer morphology. Through a first set of results, [11] demonstrates that the trap generation along the interface is quite uniform, meaning that the entire interface-spacer surface suffers from the bond dissociation. Thus, the dimensions of this surface plays an important role in the evolution of degradation.

The preceeding version of the aging compact model proposed in [8] (HiCuM AL V2.0) has demonstrated good accuracy compared to the measurements under both static and dynamic stress conditions. Since a circuit is often designed using different device geometries, a scaled formulation for HCD appears to be the next step necessary toward circuit reliability simulation. A scalable aging model has already been proposed in [10] which is based on a different physical background, the lucky electron model.

In continuation of our previous approach, the current paper introduces an extension of the previous aging compact model (HiCuM AL V2.0) presented in [8] incorporating the new scaling rules developed in accordance with the emitter dimensions and the EB spacer morphology (HiCuM AL V3.0). The rest of this paper is organized as follows; Section II focuses on the physical origin of hot-carrier degradation studied through electrical measurements and TCAD based simulations; Section III demonstrates the scalability of the degradation mechanism using various emitter dimensions; Section IV describes the scalable compact model formulation and the hydrogen diffusion mechanism; Section V presents an extraction procedure for the aging model parameters; Section VI validates the simulation results for a wide range of aging tests and devices under test (DUTs).

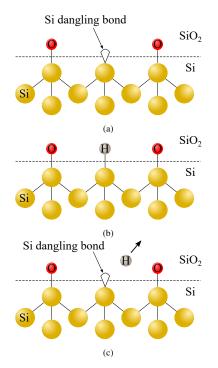

Figure 1: (a) Si dangling bond creation at the  $Si/SiO_2$  interface, (b) Incorporation of hydrogen atoms for passivation of dangling bonds and (c) Interface trap creation and hydrogen diffusion due to hot-carrier mechanism

#### 2. Physical origin of hot-carrier degradation

#### 2.1. Description

The structural disorders at the Si/SiO<sub>2</sub> interface lead to the creation of silicon dangling bonds as illustrated

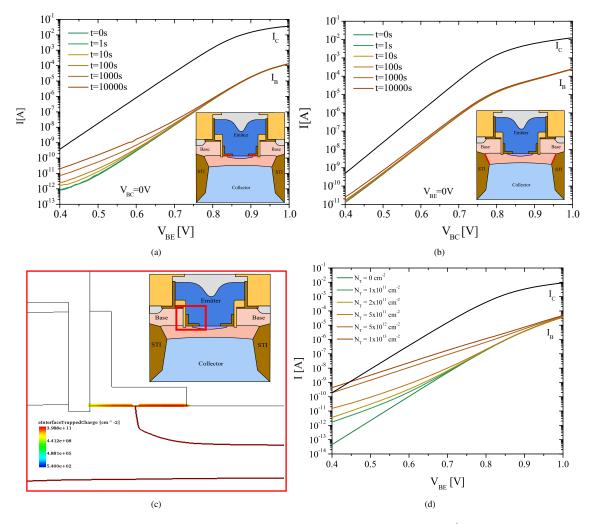

Figure 2: (a) Forward and (b) Reverse Gummel plots for a stress condition of  $V_{CB} = 2V$  and  $J_E = 0.46 \text{mA}/\mu\text{m}^2$  at different stress times, (c) TCAD structure from the inset [12] showing the addition of traps at the EB spacer interface and (d) corresponding TCAD electrical simulations results for various trap densities

in figure 1a. In order to reduce carrier-trapping in this particular region, these dangling bonds are passivated by integrating hydrogen atoms [13], as illustrated in figure 1b. However, due to low binding energy of Si-H bonds (2.3eV compared to 3.1eV for Si-O<sub>2</sub> bonds [14]), hot-carriers can gain sufficient energy to break these passivated bonds. The remaining Si dangling bonds can thus act as interface traps while the hydrogen released from these bonds diffuse away from the interface, as shown in figure 1c. In SiGe HBTs, these trap states can be located at the EB spacer or at the Shallow-Trench-Isolation (STI) oxide interface which produces an excess non-ideal base current through the Shockley-Read-Hall (SRH) recombination [13].

#### 2.2. Traps location

Since two regions can possibly be impacted by HCD, a dedicated set of measurements must be set up to discriminate the traps created at the EB spacer from the ones created at the STI. Thus, mixed-mode aging tests have been performed on a 55nm BiCMOS technology with several in-between measurements of forward (see figure 2a) and reverse (see figure 2b) Gummel plots.

In figure 2a, a large increase of the base current is observed that implies the creation of traps near the BE junction. On the contrary, the weak increase of the base current in figure 2b indicates that the trap creation close to the BC junction is less significant. Therefore, the region that principally contributes to the increase of the base current is the EB spacer oxide interface. Complimentarily, TCAD simulations [4] were performed on a simulated structure featuring this technology where various trap densities  $N_T$  were introduced at the EB spacer interface, as shown in figure 2c. As observed from the forward Gummel TCAD simulations in figure 2d, introducing traps in the EB spacer region leads to an increase of the base current at low  $V_{BE}$  (while the collector current remains unchanged) which is consistent with the aging test results.

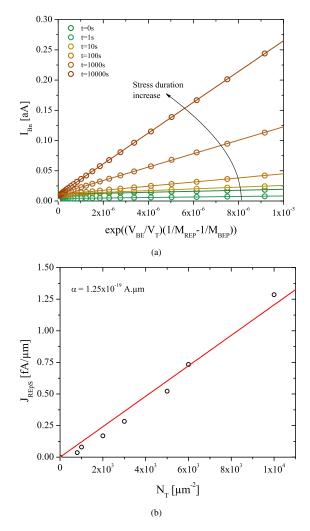

Figure 3: (a) Normalized base current at emitter periphery,  $I_{Bn}$ , extracted from measurements for a stress condition of  $V_{CB}=2V$  and  $J_E=0.46\text{mA}/\mu\text{m}^2$  at different stress times and (b)  $J_{REDS}$  evolution extracted from TCAD simulations allowing the extraction of the proportionality coefficient  $\alpha$

#### 2.3. Compact model analysis

From the point of view of compact models such as HICUM [15], the creation of traps at the  $Si/SiO_2$  interface can be attributed to the modification of a specific

base current parameter, the peripheral B-E recombination saturation current. Since only the region around the emitter periphery is impacted by HCD, the effect of degradation in the internal base-emitter current parameters can be neglected. Thus, the base current under forward operation conditions outside the avalanche regime can be expressed by equation (1) [15].

$$I_{B} = I_{BEpS} e^{\left(\frac{V_{BE}}{M_{BEP}V_{T}} - 1\right)} + I_{REpS} e^{\left(\frac{V_{BE}}{M_{REP}V_{T}} - 1\right)}$$

(1)

where  $I_{BEpS}$  is the peripheral B-E saturation current, M<sub>BEP</sub> is the peripheral B-E current ideality factor,  $I_{REpS}$ is the peripheral B-E recombination saturation current and M<sub>REP</sub> is the peripheral B-E recombination current ideality factor.

A normalized expression of the base current,  $I_{Bn}$ , is obtained using equation (2). From the measurements presented in figure 2a, the  $I_{Bn}$  parameter is extracted at different stress duration and is plotted against  $e^{\left(\frac{V_{BE}}{V_T}\left(\frac{1}{M_{REP}}-\frac{1}{M_{BEP}}\right)\right)}$  in figure 3a. As observed from this plot, while the point of intersection of the linear regression lines remains the same, the slope increases with stress time. Therefore, the parameter impacted by HCD, following equation (2), is the parameter  $I_{REPS}$  [4, 8, 10].

$$I_{Bn} = \frac{I_B}{e^{\left(\frac{V_{BE}}{M_{BEP}V_T} - 1\right)}} = I_{BEpS} + I_{REpS} e^{\left(\frac{V_{BE}}{V_T} \left(\frac{1}{M_{REP}} - \frac{1}{M_{BEP}}\right)\right)}$$

(2)

In addition, we used TCAD simulations together with HICUM simulations to correlate the increase of  $I_{REpS}$  with that of the density of traps at the spacer interface for a given geometry. To develop a scalable formulation of the degradation mechanism, the  $I_{REpS}$  parameter has been converted to  $J_{REpS}$  normalizing by the emitter perimeter  $P_E$ . The results are displayed in figure 3b for various trap densities depicting a linear relation between  $N_T$  and  $J_{REpS}$  which can be expressed by equation (3).

$$J_{REpS}(t) = \alpha N_T(t) \tag{3}$$

where  $\alpha$  is the proportionality coefficient extracted from the linear regression of figure 3b. This formulation introduces a geometry dependent expression for  $I_{REpS}$  as presented in equation (4).

$$I_{REpS}(t) = \alpha P_E N_T(t) \tag{4}$$

#### 3. Scalability of degradation mechanism

#### 3.1. HBT under test

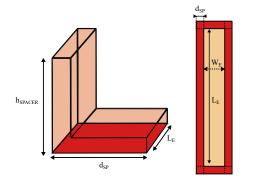

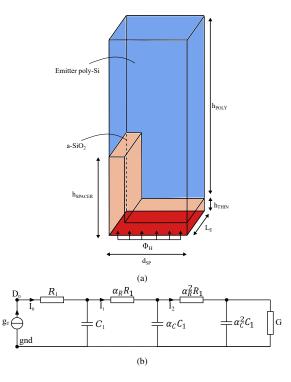

Figure 4 shows the morphology of the EB spacer for the technology under test. The area of the EB spacer interface (in red),  $A_{SPACER}$ , depends on the effective emitter length,  $L_E$ , the effective emitter width,  $W_E$ , and the EB spacer width,  $d_{SP}$ .

Figure 4: Side and top view of the emitter-base spacer of 55nm technology

| $W_E [\mu m]$ | $L_E [\mu m]$ | $A_{SPACER}$ [ $\mu m^2$ ] |

|---------------|---------------|----------------------------|

| 0.09          | 4.8           | 0.39                       |

| 0.09          | 8.8           | 0.79                       |

| 0.09          | 17.8          | 1.60                       |

Table 1: Geometry features of devices under test

The interface area,  $A_{SPACER}$ , expressed in equation (5), largely depends on the emitter perimeter  $P_E$  which is consistent with the degradation region identified in the previous section. The dimensions of the DUTs are presented in table 1 summarizing the corresponding geometry features.

$$A_{SPACER} = 2d_{SP}(L_E + W_E + 2d_{SP}) \simeq P_E d_{SP} \tag{5}$$

#### 3.2. Stress conditions

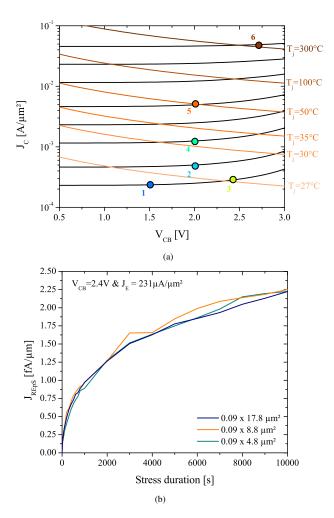

In order to verify the scalability of the hot-carrier mechanism, each device has been biased under the same stress conditions, e.g. a constant base-collector voltage  $V_{CB}$  and a constant emitter current density  $J_E$  at an ambient temperature of 25°C. The stress conditions for the three DUTs are presented in figure 5a : various  $V_{CBs}$  ranging from 1.5V to 2.7V were used to induce the electric field effect on HCD whereas various  $J_{Es}$  ranging from 200 $\mu$ A/ $\mu$ m<sup>2</sup> to 50mA/ $\mu$ m<sup>2</sup> were applied which thus led to the increase in the device temperature (T<sub>i</sub>).

Each stress condition (summarized in table 2) was carefully chosen outside the pinch-in area in order to avoid thermal and electrical instabilities [16]. Devices were submitted to aging tests for 10ks with intermediate Gummel measurements in logarithmic time intervals.

Figure 5: (a)  $J_c - V_{CB}$  curves illustrating the stress conditions applied on the three DUTs for  $T_{AMB}=25^{\circ}$ C and (b)  $J_{RE_PS}$  extraction for a stress condition of  $V_{CB}=2.4$ V and  $J_E=231\mu$ A/ $\mu$ m<sup>2</sup>

#### 3.3. Measurement results

Alike the results presented in previous studies [8, 17, 18], the  $I_{REpS}$  parameter of HICUM compact model has been extracted for each DUTs and each stress conditions (for  $V_{BE}$  ranging from 0.5V to 0.7V). The maximum values obtained for this parameter at t=10ks is equal to 22fA for the smallest and 80fA for the largest geometry, respectively. Thus, the number of created traps is greater for larger devices due to the increase of the  $A_{SPACER}$  area.

The  $J_{REpS}$ 's ( $I_{REpS}$  parameter normalized by  $P_E$ ) evolution is plotted as a function of the stress time in figure 5b. Interestingly, from this plot, it is noticeable that the values of  $J_{REpS}$  are identical for each DUT implying that the degradation mechanism is scalable with the emitter perimeter. Similar results were obtained for the other

| Number | $V_{CB}[V]$ | $\mathbf{J}_E \; [\mathbf{m}\mathbf{A}/\!\mu\mathbf{m}^2]$ | $T_j$ [°C] |

|--------|-------------|------------------------------------------------------------|------------|

| 1      | 1.5         | 0.23                                                       | 25         |

| 2      | 2           | 0.46                                                       | 27         |

| 3      | 2.4         | 0.23                                                       | 25         |

| 4      | 2           | 1.2                                                        | 31         |

| 5      | 2           | 4.6                                                        | 45         |

| 6      | 2.7         | 47                                                         | 315        |

Table 2: Details of the stress conditions depicted in figure 5a

stress conditions.

#### 4. Model formulation

#### 4.1. Reaction-diffusion theory

The bond dissociation rate can be calculated following the reaction-diffusion theory [19] as represented by equation (6).

$$\frac{dN_T}{dt} = K_F (N_F - N_T(t)) - K_R N_T(t) N_H(0, t)$$

(6)

where  $K_F$  is the trap generation rate,  $K_R$  is the trap annihilation rate,  $N_T(t)$  is the density of created traps at the interface,  $N_F$  is the density of available bonds that can break and  $N_H(0, t)$  is the volumetric density of hydrogen remaining at the Si/SiO<sub>2</sub> interface.

Following the proportionality established between  $N_T$  and  $I_{REpS}$  in section II, the compact model implementation has slightly been modified compared to [8]. In this work, it is the trap density  $N_T$  which is dynamically calculated using equation (6) while  $I_{REpS}$  parameter is determined using equation (4).

An extraction procedure for  $K_F$ ,  $K_R$  and  $N_F$  is required to obtain an accurate model response for a single device, which will be presented in section 5. However, the hydrogen diffusion dynamics must be well formulated before, in order to accurately calculate the number of hydrogen atoms remaining at the Si/SiO<sub>2</sub> interface.

#### 4.2. Diffusion mechanism

As presented in section 2.1, the free hydrogen atoms created due to the hot-carrier mechanism diffuse away from the EB spacer oxide interface and are primarily stored within the spacer oxide. The hydrogen atoms could further diffuse beyond the spacer, through the emitter poly-Si, as illustrated in figure 6a, depending on the diffusion dynamics. This last mechanism is governed by the hydrogen diffusion coefficient  $D_H$  (through  $D_0$  and  $E_a$  [8]) which is material-dependent as summarized in table 3.

Figure 6: (a) Schematic of the hydrogen diffusion volume taking into account the EB spacer oxide and the emitter poly-Si thickness and (b) RC ladder network for hydrogen diffusion modeling

In this table, three materials are considered : the amorphous SiO<sub>2</sub> (a-SiO<sub>2</sub>) located in the EB spacer, the highly-doped (N-type) poly-crystalline Si (poly-Si) in the emitter and the crystalline Si (c-Si) which is the material reference. For each material, the table lists the hydrogen diffusion parameters and the corresponding diffusion length calculated from equation (7) with a diffusion time  $t_D = 1$ s and T=300K. Since the hydrogen diffusion length for different materials varies at higher temperatures.

$$L_D = \sqrt{4D_H t_D} \tag{7}$$

| Туре                    | $D_0  [\mu m^2/s]$    | $E_a [eV]$ | $L_D  [\mu m]  (7)$   |

|-------------------------|-----------------------|------------|-----------------------|

| a-SiO <sub>2</sub> [20] | $1x10^{4}$            | 0.18       | 6.15                  |

| poly-Si [21]            | $1 \times 10^{-2}$    | 0.35       | $2.30 \times 10^{-4}$ |

| c-Si [22]               | $1x10^{6}$            | 0.48       | 0.185                 |

| This work               | $4.64 \times 10^{-1}$ | 0.48       | $1.26 \times 10^{-4}$ |

Table 3: State-of-the-art for hydrogen diffusion parameters in various materials and their corresponding diffusion length  $L_D$  for  $t_D=1s$  and T=300K

From table 3, it is evident that the hydrogen atoms diffuse significantly slower in the poly-Si compared to

the other two materials since its grain boundaries acts as efficient traps [23]. Thus, the hydrogen atoms are drastically accelerated within the thin SiO<sub>2</sub> layer until they reach the thicker poly-Si layer where it would be harder to diffuse further efficiently. Considering the time scale used for measurements, the diffusion inside the spacer is not observable since it only takes a few  $\mu$ s to cover a few tens of nanometers. As a consequence, the current work focuses on the long-term hydrogen diffusion that takes place inside the poly-Si.

#### 4.3. Diffusion model

Based on Fick's law of diffusion [24], the hydrogen diffusion from the Si/SiO<sub>2</sub> interface beyond the EB spacer oxide can be modeled using a RC ladder network, similar to the approach adopted for thermal analysis [25]. The corresponding equivalent circuit is presented in figure 6b where the diffusion volume is divided into N cells; here we have considered N=3 for the technology under test. A conductance G has been added at the end of the recursive network to model the long-term behavior (e.g. the diffusion of hydrogen beyond the poly-Si). Each resistance and capacitance of the network is calculated using equation (8).

$$\begin{cases} C_n = C_H \frac{a_C^{n-1} - a_C^n}{1 - a_C^n} \\ R_n = R_H \frac{a_R^{n-1} - a_R^n}{1 - a_R^n} \end{cases}$$

(8)

where  $C_H$  represents the storage capacity of hydrogen atoms in  $\mu$ m,  $R_H$  represents the barrier to normal lattice diffusion [26] in  $\mu$ m<sup>-1</sup>.s,  $\alpha_C$  and  $\alpha_R$  are the recursive factors for the capacitances and the resistances, respectively.

Following the assumptions made in section 4.2, the equivalent diffusion volume  $V_{DIFF}$  is only composed of the emitter poly-Si leading to equation (9).

$$V_{DIFF} = h_{POLY} A_{SPACER} \tag{9}$$

Thus, following the definition of  $C_H$  parameter, a scalable formulation can be obtained as shown in equation (10), that depends on the diffusion volume of hydrogen ( $V_{DIFF}$ ) and the interface trap generation surface ( $A_{SPACER}$ ). Furthermore, the  $R_H$  parameter is calculated using the diffusion constant of hydrogen,  $D_H$ , in the considered material as also depicted in equation (10).

$$C_H = \frac{V_{DIFF}}{A_{SPACER}}, R_H = \frac{C_H}{D_H}$$

(10)

#### 5. Parameter extraction procedure

#### 5.1. Density of Si-H bonds at the interface

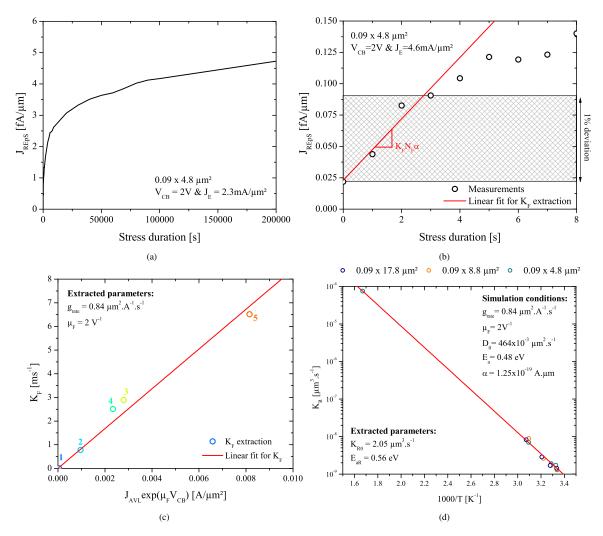

The bond dissociation is a first order mechanism represented by the first term of equation (6) in which the values of  $N_F$  and  $K_F$  have to be evaluated. The first one can be extracted from the maximum value of  $J_{REPS}$  obtained for the three devices, since it is directly related to the maximum number of traps that can be created at the interface. As observed from the aging test results the saturation of the degradation characteristics [8] has not been reached after 200ks for the stress condition presented in figure 7a. Therefore, the maximum value of  $J_{REPS}$  has been extrapolated to  $J_F=6fA/\mu m$  leading to equation (11) from which  $N_F$  can be extracted for a given technology.

$$N_F = \frac{J_F}{\alpha} \tag{11}$$

where  $\alpha$  is the coefficient extracted in section 2.3.

#### 5.2. Generation rate

The second parameter,  $K_F$ , is extracted when no annealing process can yet be observed and when the number of created traps (e.g.  $N_T$ ) is close to 0. Thus, equation (6) becomes equation (12) where the  $K_F$  can be extracted from the slope of  $dJ_{REpS}/dt$  with known values of the  $N_F$  and  $\alpha$  parameters. The aging range of time for the parameter extraction has been limited by defining a maximum deviation of 1% for  $J_{REpS}$  compared to it maximum values,  $J_F$ .

$$\frac{dJ_{REpS}}{dt} = K_F N_F \alpha \tag{12}$$

An example of the extraction method is shown in figure 7b while the extraction results obtained under five different stress conditions for a device geometry of 0.09x4.8  $\mu$ m<sup>2</sup> is presented in figure 7c. From this figure, an expression of K<sub>F</sub> has been formulated as functions of J<sub>AVL</sub> and V<sub>CB</sub>. Indeed, in [3, 8, 10], the decline of K<sub>F</sub> parameter at large current densities is due to the reduction of J<sub>AVL</sub> as demonstrated in [7].

For this reason, the expression of  $K_F$  has been modified by introducing the  $J_{AVL}$  parameter which can be obtained using the new avalanche model [7] as,

$$J_{AVL} = \frac{I_{AVL}}{A_{AVL}} \tag{13}$$

where  $I_{AVL}$  is the avalanche current and  $A_{AVL}$  is the effective emitter area for the avalanche current [27]. The detailed extraction procedure for the avalanche effect

Figure 7: (a) Evolution of  $J_{REPS}$  for a long stress duration which allows the extraction of the maximum number of Si-H bonds that can break at the interface, (b)  $K_F$  extraction example for a static stress condition, (c)  $K_F$  extraction results with corresponding linear fit leading to equation (14) for five stress conditions on a 0.09x4.8  $\mu$ m<sup>2</sup> device and (d)  $K_R$  extraction results for the three DUTs leading to an Arrehnius law

modeling is reported in [12] along with its temperature dependence.

Therefore, the modified expression of  $K_F$  is presented in equation (14) as,

$$K_F = g_{rate} J_{AVL} exp(\mu_F V_{CiBi}) \tag{14}$$

where  $g_{rate}$  is the fraction of the avalanche current density and  $\mu_F$  is an exponential factor which governs the acceleration of hot-carriers due to the electric field.

The dependence of the trap generation is more significant on  $V_{CB}$  than on the  $J_{AVL}$  parameter. Indeed only a fraction (governed by the  $g_{rate}$  parameter) of the avalanche current density will reach the spacer interface while the hot-carriers will largely be accelerated by the electric field (through  $\mu_F$  parameter) [6]. The use of  $J_{AVL}$  instead of  $J_E$  simplifies the previous expression proposed in [8].

#### 5.3. Trap annihilation rate

The second term of equation (6) corresponds to the trap annealing which depends on the number of hydrogen atoms available at the vicinity of the interface as well as on trap annihilation rate through  $K_R$ . The parameter extraction has been performed using the Levenberg-Marquardt optimization algorithm with fixed values of other model parameters (simulation conditions presented in figure 7d). The procedure has been repeated for different stress conditions and geometries leading to an

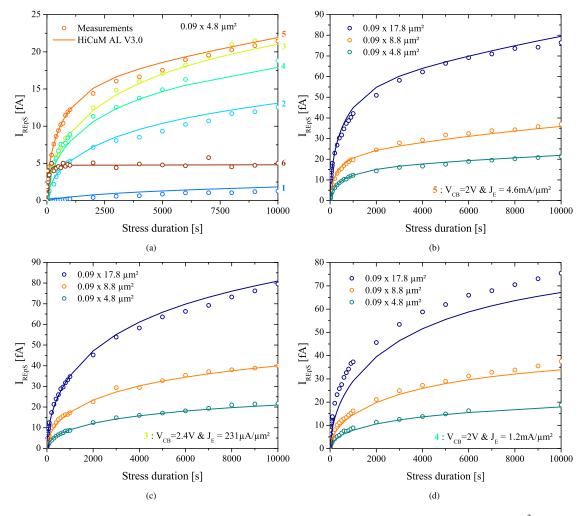

Figure 8: HiCuM-AL V3 simulations (lines) vs measurements (symbols) for (a) various aging tests (see table 2) on  $0.09x4.8 \,\mu\text{m}^2$  device and three static stress conditions in (b), (c) and (d) on all DUTs

Arrhenius law as expressed by equation (15).

$$K_R = K_{R0} exp\left(-\frac{E_{aR}}{kT_j}\right) \tag{15}$$

where  $T_j$  is the device temperature calculated using HICUM thermal node [15].

#### 6. Scalable aging compact model verification

The presented aging compact model (HiCuM AL V3.0) has first been validated on various stress conditions (see figure 5a) for a 0.09x4.8  $\mu$ m<sup>2</sup> HBT device. The comparison between the measurements (symbols) and the simulations (lines) is presented figure 8a. Very good model accuracy is achieved for various operating conditions conforming to the scaled formulation for the

trap generation rate  $K_F$  and the temperature dependence of the annealing rate  $K_R$ . Interestingly, the stress condition at high junction temperature (brown curve in fig 8a) demonstrates a dynamic equilibrium between trap generation and annihilation which is well captured by the aging model.

Next, the model has been validated for different emitter dimensions with comparable stress conditions (e.g. same  $V_{CB}$  and  $J_{AVL}$ ). A very good agreement is obtained between the measurements and the simulations for two stress conditions plotted in figure 8b and 8c. Some discrepancies are observed in figure 8d with slight under-estimations of the degradation for the two largest devices. The main explanation of these differences is that the initial value of the  $I_{REpS}$  parameter was larger than the values predicted by the model (due to the tech-

| Parameters | $\alpha$ [A]           | $D_0 \left[\mu m^2/s\right]$ | $E_a [eV]$ | $\mu_F [\mathrm{V}^{-1}]$ | $g_{rate} \ [\mu m^2.A^{-1}.s^{-1}]$ | $K_{R0} \ [\mu m^3/s]$ | $E_{aR}$ [eV] |

|------------|------------------------|------------------------------|------------|---------------------------|--------------------------------------|------------------------|---------------|

| Values     | $1.25 \times 10^{-19}$ | $4.64 \times 10^{-1}$        | 0.48       | 2.0                       | 0.84                                 | 2.05                   | 0.56          |

Table 4: Extracted model parameters for HiCuM AL V3.0 and a BiCMOS 55nm technology

nological variability between 2 dies) revealing a higher number of pre-existing traps before the beginning of aging tests. However, the scalable aging compact model demonstrates sufficient accuracy for various operating conditions and various emitter dimensions allowing its further exploitation in circuit reliability simulation.

The table 4 is provided as a summary of the extracted parameters for the scalable aging compact model formulation (HiCuM AL V3.0).

#### 7. Conclusion

In this work, we have demonstrated that HCD depends on the spacer morphology. Indeed, increasing the degradation area at the interface increases the potential, number of traps. Thus, a scalable formulation (HiCuM AL V3.0) has been proposed to enhance the former physics-based aging compact model. This new aging compact model is compatible with SiGe HBT architectures and dimensions. The aging compact model has been validated against aging tests on a 55nm BiCMOS technology confirming its accuracy against various stress conditions and geometry features. The scaled formulation can now easily be adapted for circuit simulations where scalable model cards are frequently used. Owing to its physical basis, the proposed model can provide accurate reliability predictions for circuits operating close to and beyond the SOA.

#### References

- P. Chevalier, M. Schröter, C. R. Bolognesi, V. d'Alessandro, M. Alexandrova, J. Böck, R. Flückiger, S. Fregonese, B. Heinemann, C. Jungemann, R. Lövblom, C. Maneux, O. Ostinelli, A. Pawlak, N. Rinaldi, H. Rücker, G. Wedel, T. Zimmer, Si/SiGe:C and InP/GaAsSb heterojunction bipolar transistors for THz applications, Proceedings of the IEEE 105 (6) (2017) 1035–1050. doi:10.1109/JPROC.2017.2669087.

- [2] F. M. Puglisi, L. Larcher, P. Pavan, Mixed-mode stress in silicon-germanium heterostructure bipolar transistors: Insights from experiments and simulations, IEEE Transactions on Device and Materials Reliability 19 (2) (2019) 275–282. doi: 10.1109/TDMR.2019.2912853.

- [3] G. Fischer, G. Sasso, Ageing and thermal recovery of advanced SiGe heterojunction bipolar transistors under long-term mixedmode and reverse stress conditions, Microelectronics Reliability 55 (3) (2015) 498 - 507. doi:10.1016/j.microrel.2014. 12.014.

- [4] M. Jaoul, D. Ney, D. Céli, C. Maneux, T. Zimmer, Analysis of a failure mechanism occurring in SiGe HBTs under mixed-mode stress conditions, in: 2019 IEEE 32nd International Conference on Microelectronic Test Structures (ICMTS), 2019, pp. 33–37. doi:10.1109/ICMTS.2019.8730951.

- [5] K. A. Moen, P. S. Chakraborty, U. S. Raghunathan, J. D. Cressler, H. Yasuda, Predictive physics-based TCAD modeling of the mixed-mode degradation mechanism in SiGe HBTs, IEEE Transactions on Electron Devices 59 (11) (2012) 2895–2901. doi:10.1109/TED.2012.2210898.

- [6] T. Vanhoucke, G. A. M. Hurkx, D. Panko, R. Campos, A. Piontek, P. Palestri, L. Selmi, Physical description of the mixed-mode degradation mechanism for high performance bipolar transistors, in: 2006 Bipolar/BiCMOS Circuits and Technology Meeting, 2006, pp. 1–4. doi:10.1109/BIPOL.2006.311150.

- [7] M. Jaoul, C. Maneux, D. Céli, M. Schröter, T. Zimmer, A compact formulation for avalanche multiplication in SiGe HBTs at high injection levels, IEEE Transactions on Electron Devices 66 (1) (2019) 264–270. doi:10.1109/TED.2018.2875494.

- [8] C. Mukherjee, F. Marc, M. Couret, G. Fischer, M. Jaoul, D. Céli, K. Aufinger, T. Zimmer, C. Maneux, A physical and versatile aging compact model for hot carrier degradation in SiGe HBTs under dynamic operating conditions, Solid-State Electronics 163 (2020) 107635. doi:10.1016/j.sse.2019.107635.

- [9] S. Mahapatra, R. Saikia, On the universality of hot carrier degradation: Multiple probes, various operating regimes, and different MOSFET architectures, IEEE Transactions on Electron Devices 65 (8) (2018) 3088–3094. doi:10.1109/TED.2018.2842129.

- [10] B. R. Wier, R. P. Martinez, U. S. Raghunathan, H. Ying, S. Zeinolabedinzadeh, J. D. Cressler, Revisiting safe operating area: SiGe HBT aging models for reliability-aware circuit design, in: 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2018, pp. 215–218. doi:10.1109/BCICTS.2018.8551087.

- [11] H. Kamrani, D. Jabs, V. d'Alessandro, N. Rinaldi, T. Jacquet, C. Maneux, T. Zimmer, K. Aufinger, C. Jungemann, Microscopic hot-carrier degradation modeling of SiGe HBTs under stress conditions close to the SOA limit, IEEE Transactions on Electron Devices 64 (3) (2017) 923–929. doi:10.1109/TED.2017. 2653197.

- [12] M. Jaoul, Study of HBT operation beyond breakdown voltage. definition of a safe operating area in this operation regime including the aging laws, Ph.D. thesis, University of Bordeaux (2020).

- [13] N. Rinaldi, M. Schröter, Silicon-Germanium Heterojunction Bipolar Transistors for mm-Wave Systems: Technology, Modeling and Circuit Applications, River Publishers, 2018. doi: 10.13052/rp-9788793519602.

- [14] D. J. DiMaria, J. W. Stasiak, Trap creation in silicon dioxide produced by hot electrons, Journal of Applied Physics 65 (6) (1989) 2342–2356. doi:10.1063/1.342824.

- [15] M. Schröter, A. Chakravorty, Compact Hierarchical Bipolar Transistor Modeling with HiCuM, World Scientific, 2010. doi: 10.1142/7257.

- [16] M. Jaoul, D. Céli, C. Maneux, T. Zimmer, Measurement based accurate definition of the SOA edges for SiGe HBTs, 2019 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and

Technology Symposium (BCICTS).

- [17] C. Mukherjee, T. Jacquet, G. G. Fischer, T. Zimmer, C. Maneux, Hot-carrier degradation in SiGe HBTs: A physical and versatile aging compact model, IEEE Transactions on Electron Devices 64 (12) (2017) 4861–4867. doi:10.1109/TED.2017. 2766457.

- [18] T. Jacquet, G. Sasso, A. Chakravorty, N. Rinaldi, K. Aufinger, T. Zimmer, V. d'Alessandro, C. Maneux, Reliability of high-speed SiGe:C HBT under electrical stress close to the SOA limit, Microelectronics Reliability 55 (9) (2015) 1433 – 1437, proceedings of the 26th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis. doi:10.1016/j.microrel.2015.06.092.

- [19] K. O. Jeppson, C. M. Svensson, Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices, Journal of Applied Physics 48 (5) (1977) 2004–2014. doi: 10.1063/1.323909.

- [20] D. L. Griscom, Diffusion of radiolytic molecular hydrogen as a mechanism for the post-irradiation buildup of interface states in SiO2-on-Si structures, Journal of Applied Physics 58 (7) (1985) 2524–2533. doi:10.1063/1.335931.

- [21] N. H. Nickel, I. E. Beckers, Hydrogen migration in doped and undoped polycrystalline and microcrystalline silicon, Phys. Rev. B 66 (2002) 075211. doi:10.1103/PhysRevB.66.075211.

- [22] S. Bédard, L. J. Lewis, Diffusion of hydrogen in crystalline silicon, Physical Review B 61 (15) (2000) 9895–9898. doi: 10.1103/physrevb.61.9895.

- [23] W. B. Jackson, N. M. Johnson, C. C. Tsai, I. Wu, A. Chiang, D. Smith, Hydrogen diffusion in polycrystalline silicon thin films, Applied Physics Letters 61 (14) (1992) 1670–1672. doi:10. 1063/1.108446.

- [24] D. A. Fick, V. on liquid diffusion, The London, Edinburgh, and Dublin Philosophical Magazine and Journal of Science 10 (63) (1855) 30–39. doi:10.1080/14786445508641925.

- [25] M. Couret, G. Fischer, S. Frégonése, T. Zimmer, C. Maneux, Physical, small-signal and pulsed thermal impedance characterization of multi-finger SiGe HBTs close to the SOA edges, in: 2019 IEEE 32nd International Conference on Microelectronic Test Structures (ICMTS), 2019, pp. 154–159. doi: 10.1109/ICMTS.2019.8730964.

- [26] G. Pressouyre, I. Bernstein, An electrical analog model of hydrogen trapping in iron alloys, Corrosion Science 18 (9) (1978) 819 833. doi:10.1016/0010-938X(78)90018-5.

- [27] D. Celi, Review of some HICUM geometry scaling laws: Issue and proposal, in: 7 th HICUM Workshop, Dresden, 2007.