## Improvement of the electrical performance of $Au/Ti/HfO\ 2$ /Ge 0.9 Sn 0.1 p-MOS capacitors by using interfacial layers

T. Haffner,, M.A. Mahjoub,, S. Labau,, J. Aubin,, J.M. Hartmann,, G. Ghibaudo,, S. David,, B. Pelissier,, F. Bassani,, B. Salem

## ▶ To cite this version:

T. Haffner, M.A. Mahjoub, S. Labau, J. Aubin, J.M. Hartmann, et al.. Improvement of the electrical performance of Au/Ti/HfO 2 /Ge 0.9 Sn 0.1 p-MOS capacitors by using interfacial layers. Applied Physics Letters, 2019, 115 (17), pp.171601. 10.1063/1.5121474. hal-03027755

## HAL Id: hal-03027755 https://cnrs.hal.science/hal-03027755v1

Submitted on 27 Nov 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Improvement of the electrical performance of Au/Ti/HfO<sub>2</sub>/Ge<sub>0.9</sub>Sn<sub>0.1</sub> p-MOS capacitors by using interfacial layers

Cite as: Appl. Phys. Lett. **115**, 171601 (2019); https://doi.org/10.1063/1.5121474 Submitted: 26 July 2019 . Accepted: 06 October 2019 . Published Online: 21 October 2019

T. Haffner, M. A. Mahjoub, S. Labau, D. J. Aubin, J. M. Hartmann, D. G. Ghibaudo, S. David, B. Pelissier, D. F. Bassani, and D. B. Salem

### ARTICLES YOU MAY BE INTERESTED IN

Alkali-metal spin maser for non-destructive tests

Applied Physics Letters 115, 173502 (2019); https://doi.org/10.1063/1.5121606

Polycrystalline Co<sub>2</sub>Mn-based Heusler thin films with high spin polarization and low magnetic damping

Applied Physics Letters 115, 172401 (2019); https://doi.org/10.1063/1.5121614

Comprehensive insights into effect of van der Waals contact on carbon nanotube network field-effect transistors

Applied Physics Letters 115, 173503 (2019); https://doi.org/10.1063/1.5100011

## Your Qubits. Measured.

Meet the next generation of quantum analyzers

- Readout for up to 64 qubits

Operation at up to 8.5 GHz

- Operation at up to 8.5 GHz, mixer-calibration-free

Signal optimization with minimal latency

Find out more

## Improvement of the electrical performance of Au/Ti/HfO<sub>2</sub>/Ge<sub>0.9</sub>Sn<sub>0.1</sub> p-MOS capacitors by using interfacial layers

Cite as: Appl. Phys. Lett. **115**, 171601 (2019); doi: 10.1063/1.5121474 Submitted: 26 July 2019 · Accepted: 6 October 2019 · Published Online: 21 October 2019

T. Haffner, M. A. Mahjoub, S. Labau, J. Aubin, D. M. Hartmann, G. Ghibaudo, Es. David, B. Pelissier, F. Bassani, D. and B. Salem D.

#### **AFFILIATIONS**

- <sup>1</sup>Univ. Grenoble Alpes, CNRS, CEA/LETI Minatec, LTM, F-38054 Grenoble, France

- <sup>2</sup>Univ. Grenoble Alpes, CEA/LETI, MINATEC Campus, F-38054 Grenoble, France

- <sup>3</sup>Univ. Grenoble Alpes, CNRS, Grenoble INP, IMEP-LaHC, F-38000 Grenoble, France

#### **ABSTRACT**

The impact of different interfacial layers (ILs) on the electrical performances of  $Au/Ti/HfO_2/Ge_{0.9}Sn_{0.1}$  metal oxide semiconductor (MOS) capacitors is studied. Parallel angle resolved x-ray photoelectron spectroscopy measurements show that germanium diffuses into the  $HfO_2$  layer when no IL is used. This results in an increase in the tin content at the interface and a high interface state density. We demonstrate that the use of an IL prevents germanium and  $HfO_2$  intermixing and improves the electrical performance of MOS capacitors. Several ILs are studied such as alumina  $(Al_2O_3)$  and plasma oxidized GeSn  $(GeSnO_x)$  prior to  $HfO_2$  deposition. C–V measurements correlated with simulations made by a customized analytical model indicate an interface state density of  $5 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  for the  $HfO_2/GeSnO_x/Ge_{0.9}Sn_{0.1}$  gate stack. This result is promising for the integration of high mobility GeSn channels in CMOS devices.

Published under license by AIP Publishing. https://doi.org/10.1063/1.5121474

The introduction of materials with carrier mobilities higher than silicon (Si) is important to further improve the performance of metal oxide semiconductor field effect transistors (MOSFETs). In this respect, the germanium tin (GeSn) alloy is a very promising candidate since it exhibits a direct and low bandgap for Sn contents >7.1%, has high carrier mobilities,<sup>2,3</sup> and belongs to group-IV semiconductors. These assets make it interesting for its introduction as a channel material into pFET transistors. Recently, several research groups reported on the growth of high-quality GeSn epitaxial layers on Si wafers by means of chemical vapor deposition (CVD)<sup>4-7</sup> and molecular beam epitaxy (MBE).<sup>8,9</sup> This breakthrough enables development of devices such as high ON-current MOSFETs, 10-14 Schottky-barrier FETs (SBFETs), or tunnel FETs (TFETs). 15-18 However, the device performance does not depend only on the material properties of the channel, but also on the electrostatic control of the gate. Hence, the fabrication of high-k/GeSn gate stacks with a good interfacial quality is key to obtaining high performance GeSn-based devices.

Atomic layer deposition (ALD) is the most suitable technique for the deposition of high-k materials such as  $Al_2O_3$ ,  $HfO_2$ , and  $ZrO_2$  at a low temperature ( $\leq 250$  °C) with excellent uniformity and well controlled

thicknesses. Nevertheless, this deposition process results in a high surface state density ( $D_{\rm it}$ ), degrading the electrical performance of pMOS capacitors. For this, wet chemical treatments and/or the addition of an interfacial layer (IL)<sup>19</sup> were proposed prior to the high-k deposition in order to reduce the  $D_{\rm it}$  and enhance the reliability of the manufactured devices. Several studies, such as those of Gupta et al, <sup>14</sup> Han et al, <sup>16</sup> and Mahjoub et al, <sup>20</sup> focused on the impact of wet cleaning on devices. Meanwhile, Wirths et al.<sup>21</sup> evaluated the interface quality for different high-k stacks on GeSn and strained Ge. However, that study focused mainly on strained Ge with an incomplete investigation of high-k/GeSn stacks.

In this work, we report on the fabrication of various  $Ge_{0.9}Sn_{0.1}$  based p-type MOS capacitors with different dielectric stacks. These structures will be investigated in order to determine which dielectric stack yields the best interface with the  $Ge_{0.9}Sn_{0.1}$  channel. High-resolution transmission electron microscopy (HR-TEM) is used to evaluate the morphology and quality of the dielectric/GeSn stacks. Capacitance–voltage (C–V) measurements together with theoretical calculations are performed to extract the  $D_{it}$  for each p-type MOS capacitor. Finally, parallel angle-resolved X-ray photoelectron spectroscopy (pAR-XPS) is used to investigate the physical and chemical

a) Author to whom correspondence should be addressed: bassem.salem@cea.fr

properties of the dielectric/GeSn interfaces in relation to their electrical characteristics.

The 50 nm thick Ge<sub>0.9</sub>Sn<sub>0.1</sub> layer used in this work was grown on a 2.5  $\mu$ m thick Ge strain relaxed buffer (Ge SRB) grown itself on an Si (100) substrate in a 200 mm Epi Centura 5200 reduced pressure chemical vapor deposition (RP-CVD) cluster tool from Applied Materials. Further details can be found elsewhere.<sup>22</sup> The high-k layers were deposited at 250 °C in a Fiji–Savannah (ALD) tool. Trimethylaluminium (TMA, Epichem, 99.9%), tetrakis(dimethyllamido)hafnium (TDMAH), and de-ionized water (Di-H<sub>2</sub>O, Epichem, 99.9%), were used as the aluminum, hafnium, and oxygen precursors, respectively. GeSnO<sub>x</sub> was formed with an *in situ* oxygen plasma prior to the high-k deposition. After high-k dielectric deposition, 5 nm of titanium and 145 nm of gold were evaporated in a MEB550 tool from PLASSYS in order to form the MOS structures with conventional photolithography and liftoff steps.

In this work, four samples were fabricated with different dielectric stacks. Prior to this process, all samples underwent the same wet chemical treatment which consisted of a surface degrease, a dip in HF for 1 min, and a dip in  $(NH_4)_2S$  for 30 min.<sup>20</sup> The dielectric stacks of the four samples are detailed in Table I.

XPS and pAR-XPS analysis were performed on a customized Thermo Fisher Scientific Theta 300 system with ultrahigh vacuum conditions ( $<1\times10^{-8}$  Pa) equipped with an X-ray source using a monochromatic aluminum anode (1486.6 eV). The analyzer has a two-dimensional detector, allowing parallel acquisition at eight emission angular ranges of 7.5° from 20° to 80° without any tilt of the sample. HR-TEM imaging was performed on a TEM TECNAI from Thermo Fisher Scientific with an incident electron beam of 200 keV. For the HRTEM observation, a thin lamella of the MOS structure was prepared by using a Helios NanoLab 450s FIB-SEM tool from FEI (Fisher Scientific), combining a Ga<sup>+</sup> focused ion beam and an electron beam. C–V measurements were carried out with a Keithley 4200A SCS analyzer.

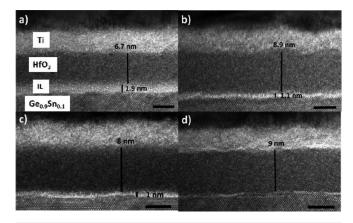

Figure 1 shows the cross-sectional HRTEM images of samples S1, S2, S3, and S4. The different dielectric layers deposited on the crystalline GeSn layer are clearly seen. The experimental thickness of each layer is in a good agreement with the expected one. In addition, a certain roughness at the GeSn/dielectric interface can be observed for all samples. It could be due to the initial surface roughness of the asgrown GeSn layer [the surface root mean square (rms) roughness is indeed equal to 0.43 nm for the  $5 \times 5 \ \mu m^2$  AFM images<sup>6</sup>].

Capacitance-voltage measurements were carried out in order to evaluate the impact of the different dielectric stacks on the electrical properties of the MOS capacitors.

To suppress the contribution of the series resistance to the C–V curves, a correction of the measured capacitance ( $C_{\rm m}$ ) has been applied using the following formula:<sup>22</sup>

TABLE I. Description of the samples investigated in this work.

| Sample name | Description of the gate stacks                                                           |  |  |  |

|-------------|------------------------------------------------------------------------------------------|--|--|--|

| S1          | GeSn/1 nm-GeSnO <sub>x</sub> /1 nm-Al <sub>2</sub> O <sub>3</sub> /7 nm-HfO <sub>2</sub> |  |  |  |

| S2          | $GeSn/1 nm-Al_2O_3/9 nm-HfO_2$                                                           |  |  |  |

| S3          | $GeSn/1 nm-GeSnO_x/8 nm-HfO_2$                                                           |  |  |  |

| S4          | $GeSn/9 nm-HfO_2$                                                                        |  |  |  |

**FIG. 1.** Cross-sectional HR-TEM images of (a) S1, 1 nm-GeSnO<sub>x</sub>/1 nm-Al<sub>2</sub>O<sub>3</sub>/7 nm-HfO<sub>2</sub>, (b) S2, 1 nm-Al<sub>2</sub>O<sub>3</sub>/9 nm-HfO<sub>2</sub>, (c) S3, 1 nm-GeSnO<sub>x</sub>/8 nm-HfO<sub>2</sub>, and (d) S4, 9 nm-HfO<sub>2</sub> gate stacks. The scale bars are 5 nm for all images.

$$C_c = \frac{\left(G_m^2 + \omega^2 C_m^2\right) C_m}{a^2 + \omega^2 C_m^2},\tag{1}$$

where  $C_c$ ,  $C_m$ , and  $G_m$  are the corrected capacitance, the measured capacitance, and the measured conductance, respectively, and  $\omega=2\pi f$

$$a = G_m - \left(G_m^2 + \omega^2 C_m^2\right) R_s \tag{2}$$

with

$$R_{s} = \frac{G_{ma}}{G_{ma}^{2} + \omega^{2} C_{ma}^{2}},$$

(3)

where  $G_{\text{ma}}$  and  $C_{\text{ma}}$  are the conductance and the capacitance measured in strong accumulation, respectively.

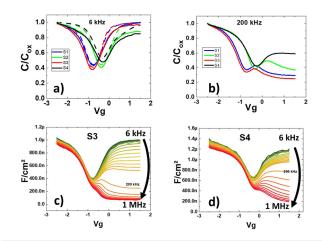

Figures 2(a) and 2(b) show the normalized C-V characteristics for all samples at 6 and 200 kHz, respectively. The corrected C-V curves from 6 kHz up to 1 MHz are shown in Figs. 2(c) and 2(d) for samples

**FIG. 2.** (a) Normalized *C–V* characteristics (scattered) and simulation (full line) of all samples measured at 6 kHz. (b) Normalized *C–V* characteristics of all samples measured at 200 kHz. Frequency dependence of the corrected *C–V* curves for samples (c) S3 and (d) S4, respectively.

S3 and S4, respectively. The capacitors' gate leakage current does not exceed  $5 \times 10^{-6}$  A cm<sup>-2</sup> at -2.5 V. The capacitance frequency dispersions measured in accumulation at -2.5 V between 6 kHz and 1 MHz are equal to 9.7%, 7.7%, 11.4%, and 13.9% for samples S1, S2, S3, and S4, respectively. Frequency dispersion is usually caused by border traps near the oxide/semiconductor interface in Ge MOSCAPs. 23,24 Indeed, the presence of traps close to the interface changes the tunneling time constant, resulting in frequency dispersion.<sup>25</sup> In addition, several important parameters can be extracted from these C-V measurements such as the interface state density, the flatband voltage, and the minority carrier generation time. The conductance method, described by Nicollian and Goetzberger, <sup>26</sup> is generally used to extract the interface state density as it provides a precise measurement. However, in the case of a low bandgap material such as GeSn, this method becomes less effective due to the minority carrier response (e here) leading to higher uncertainties. Hence, C-V measurements were simulated using a customized analytical C-V model described elsewhere. <sup>20</sup> The model includes a quasicontinuum of interface traps with a constant energy density over the bandgap and minority carrier generation time.

Table II provides the extracted interface state density, the minority carrier generation time ( $\tau_{min}$ ), and the flatband voltage for the various samples. As expected, the sample with no interfacial layer (S4) exhibits a high interface state density, i.e.,  $6\times 10^{12}~\text{eV}^{-1}~\text{cm}^{-2}$ . In contrast, samples S1 and S3 with a GeSnOx interfacial layer have the lowest interface state densities,  $7\times 10^{11}~\text{eV}^{-1}~\text{cm}^{-2}$  and  $5\times 10^{11}~\text{eV}^{-1}~\text{cm}^{-2}$ , i.e., values even better than that of sample S2 with an Al<sub>2</sub>O<sub>3</sub> IL having a D<sub>it</sub> of  $9\times 10^{11}~\text{eV}^{-1}~\text{cm}^{-2}$ . However, the interfacial layer does not affect only the interface quality. Indeed, all samples have different minority carrier generation times, as seen on the normalized C–V curves at 200 kHz in Fig. 2(b). The minority carrier generation times ( $\tau_{min}$ ) were simulated in our model with the following expression:

$$C_{min}(\tau_{min}) = \frac{C_{min}}{1 + (2\pi * f * \tau_{min})^2},$$

(4)

where  $C_{\rm min}$  is the quasistatic minority carrier capacitance. The samples with  ${\rm GeSnO_x}$  at the interface (S1 and S3) present similar values of  $\approx 9~\mu {\rm s}$ . The sample with  ${\rm Al_2O_3}$  (S2) has a shorter minority generation time  $\tau_{\rm min}=7~\mu {\rm s}$ . The minority carrier generation time is the fastest in the sample without any interlayer (S4), with  $\tau_{\rm min}=4~\mu {\rm s}$  only. Schulte-Braucks *et al.*<sup>27</sup> studied the inversion response as a function of the Sn content in metal/high-k/GeSn MOS capacitors. They showed that higher Sn contents resulted in higher minority carrier generation times. The different  $\tau_{\rm min}$  in our samples could be explained by interfacial tin concentration differences depending on the interlayer used although the same GeSn layer was used for all MOS capacitors. The GeSn lattice at the interface is apparently modified during the ALD process.

Finally, it should be noted that nonoxidized samples S2 and S4 exhibit Vfb values close to those of the ideal ones  $\approx$  -0.61 V.<sup>28</sup>

TABLE II. Extracted parameters of all samples from the C-V simulations.

| -                                                               | S1                              | S2                        | S3                        | S4                            |

|-----------------------------------------------------------------|---------------------------------|---------------------------|---------------------------|-------------------------------|

| $\frac{D_{it} (eV^{-1} cm^{-2})}{\tau_{min} (\mu s)}$ $Vfb (V)$ | $7 \times 10^{11}$ $8.5$ $-1.2$ | $9 \times 10^{11}$ 7 -0.8 | $5 \times 10^{11}$ 9 -1.2 | $6 \times 10^{12}$ $4$ $-0.6$ |

Instead, oxidized samples S1 and S3 show more negative Vfb values due to extra positive charges or compensation of the existing negative charges. Indeed, S. Gupta *et al.*<sup>29</sup> investigated the GeSnO<sub>2</sub>/Ge<sub>0.92</sub>Sn<sub>0.08</sub> and GeO<sub>2</sub>/Ge<sub>0.92</sub>Sn<sub>0.08</sub> interfaces by deep level transient spectroscopy (DLTS) and saturation photovoltage (SPV). In the case of the GeSnO<sub>2</sub>/GeSn interface, they demonstrated that the majority of the traps were positively charged close to the valence band edge. Given the global decrease of D<sub>it</sub> when GeSnO<sub>x</sub> is used, it can be deduced that surface oxidation prior to high-*k* deposition does neutralize the existing negatively charged traps. It should also be mentioned that, in our samples, no significant hysteresis was observed during the forward and backward gate voltage sweep, indicating that border traps have no major impact in both oxidized and nonoxidized cases.

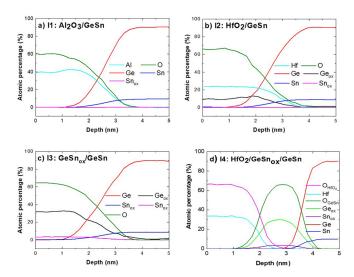

To better understand the electrical behavior of each GeSn pMOS capacitor, an in-depth investigation of the chemical composition and the different oxidation states of each compound at the dielectric/GeSn interface is necessary. For this, the XPS experiments were carried out on four dedicated samples using the same conditions as described in Table I. The four samples consist of 2 nm of Al<sub>2</sub>O<sub>3</sub>, 2 nm of HfO<sub>2</sub>, 2 nm of GeSnO<sub>x</sub> on Ge<sub>0.9</sub>Sn<sub>0.1</sub>, and 2 nm of HfO<sub>2</sub>/GeSnO<sub>x</sub>/Ge<sub>0.9</sub>Sn<sub>0.1</sub>, called I1, I2, I3, and I<sub>4</sub>, respectively. Calibration of the XPS spectra was done by using the main C1s peak at 285 eV of the adventitious carbon which is adsorbed on the samples surface during the transfer, and all recorded XPS peaks were fitted using a Shirley background.

Figure 3 shows the fitted Ge3d and Sn3d peaks of I1-I3 samples. The Ge3d peak fitting of different samples shows the presence of

**FIG. 3.** XPS spectra [(a), (c), and (e)] of Ge3d and [(b), (d), and (f)] Sn3d $_{5/2}$  for  $11(Al_2O_3/GeSn10\%)$ ,  $12(HfO_2/GeSn10\%)$ , and  $13(GeSnO_3/GeSn10\%)$ , respectively.

Ge3d<sub>3/2</sub> and Ge3d<sub>5/2</sub> peaks at 28.7 and 29.7 eV, which are the signature of Ge in the GeSn layer. Likewise, the tin (Sn) spectra of all samples show a peak at 484.8 eV, Sn3d<sub>5/2</sub>, which is attributed to the Sn atoms in the Ge<sub>0.9</sub>Sn<sub>0.1</sub> layer. For I1, XPS reveals the absence of Ge oxidation states [Fig. 3(a)] and shows a small peak at 485.6 eV [Fig. 3(b)] associated with the Sn<sup>2+</sup> state corresponding to the Sn-O bond. The latter highlights a good compatibility between Al<sub>2</sub>O<sub>3</sub> and Ge<sub>0.9</sub>Sn<sub>0.1</sub> and a high interface quality. For I2, there are two additional subpeaks, shifted from the Ge3d peak by 1.7 and 3.5 eV toward higher binding energies [Fig. 3(c)]. These peaks are attributed to the  $Ge^{2+}$  and  $Ge^{4+}$  states, which correspond to GeO and GeO2, respectively. Moreover the Sn3d<sub>5/2</sub> [Fig. 3(d)] shows the presence of two peaks at 485.6 and 486.1 eV, corresponding to the Sn<sup>2+</sup> and Sn<sup>4+</sup> states, respectively. These results indicate the low quality of the HfO2/Ge0.9Sn0.1 interface due to the presence of a mixture of different oxides. Moreover, I2 contains GeO which is known to be volatile. For I3, only the Ge4+ state corresponding to the Ge-O<sub>2</sub> bond was detected [Fig. 3(e)]. The Sn3d<sub>5/2</sub> [Fig. 3(f)] shows the presence of an intense peak at 486.2 eV corresponding to the Sn4+ state and a relatively small peak at 486.1 eV attributed to the Sn<sup>2+</sup>. Thus, these results show the chemical homogeneity of the GeSnO<sub>x</sub> layer, with a domination of 4+ states for Ge and Sn, which corroborates the lower value of Dit of  $5 \times 10^{11}$  eV<sup>-1</sup> cm<sup>-2</sup> measured for sample S3. For I4, XPS measurements (not presented here) show the same behavior of the GeSnO<sub>x</sub> layer as I3.

To summarize, the XPS results demonstrate that the  $GeSnO_x/GeSn$  interface is chemically stable in I1, I3, and I4 samples. However, I2 ( $HfO_2/Ge_{0.9}Sn_{0.1}$ ) has a mixture of Ge and Sn oxidation states, likely due to a reaction between  $HfO_2$  precursors and the GeSn surface during the ALD of  $HfO_2$ . To clarify these points, pAR-XPS experiments were performed on I1-I4 samples. Hf4d, Ge3d,  $Sn3d_{5/2}$ , Al2p, and O1s spectra were recorded at emission angles from 23.5° to 75.25° with respect to the normal of the sample. Using these spectra, the composition depth profiles of I1-I3 were calculated using the Avantage<sup>®</sup> software based on the maximum entropy method.  $^{30,31}$

Figure 4 shows the in-depth chemical profiles of I1 [Fig. 4(a)], I2 [Fig. 4(b)], I3 [Fig. 4(c)], and I4 [Fig. 4(d)], respectively. Regardless of the sample, the GeSn composition is in a good agreement with the expected value (90% Ge and 10% Sn). For I1, the stoichiometry of the Al<sub>2</sub>O<sub>3</sub> layer is the expected one, with Ge<sub>ox</sub> or Sn<sub>ox</sub> below the detection limit at the interface. This result explains the low Dit value obtained on S2 (see Table II). For I2, the depth profile shows a diffusion of Geox within the HfO2 layer. Such a behavior was already reported for HfO2/ Ge or SiGe by several groups<sup>32-34</sup> and could be responsible for the dielectric permittivity, leakage current, and interface state density issues.<sup>35</sup> In the case of GeSn, Ge diffusion into the HfO<sub>2</sub> layer results in a modification of the Ge<sub>1-x</sub>Sn<sub>x</sub> stoichiometry close to the interface and, thus, a Sn segregation. This hypothesis is well supported by CV measurements and the theoretical simulations which give a higher Dit value (see Table II). In the I3 sample case, the chemical profile shows the chemical stoichiometry of GeSnO2 perfectly. Moreover, the I4 depth profile [Fig. 4(d)] does not reveal any intermixing of HfO2 with the Ge or Sn compound which provides evidence that in the case of GeSnOx passivation, the interface is stable and the Ge out-diffusion is suppressed.

The pAR-XPS results are in a agreement with the Dit values (Table II) which shows that the sample with  $GeSnO_x$  and  $Al_2O_3$  interface layers has a lower Dit. The superiority of the  $GeSnO_x/GeSn$  compared to the  $Al_2O_3/GeSn$  interface can be explained by the fact that the

**FIG. 4.** Chemical depth profiles of (a) 11 (Al<sub>2</sub>O<sub>3</sub>/GeSn), (b) 12 (HfO<sub>2</sub>/GeSn), (c) GeSn<sub>ox</sub>/GeSn, and (d) 14 (HfO<sub>2</sub>/GeSn<sub>ox</sub>/GeSn). The relative concentrations of aluminum (Al), hafnium (Hf), germanium (Ge), tin (Sn), germanium oxide (Ge<sub>ox</sub>), tin oxide (Sn<sub>ox</sub>), and oxygen are plotted as functions of depth.

$GeSnO_x$  layer ensures a natural chemical continuity with the GeSn surface which is not the case with  $Al_2O_3$ .

The use of interlayers in HfO<sub>2</sub>/GeSn p-MOS capacitors was investigated in order to improve their electrical performance. It was found that the direct deposition of HfO<sub>2</sub> by ALD on GeSn resulted in Ge diffusion through the HfO<sub>2</sub> layer, altering the semiconductor and dielectric properties and leading to a high interface state density. We showed that the *in situ* formation of an interlayer GeSnO<sub>x</sub> layer prevented the intermixing of HfO<sub>2</sub> and Ge. It was found that the use of this interlayer drastically reduced the interface state density, with the obtained values as low as  $5 \times 10^{11} \ {\rm eV^{-1} \ cm^{-2}}$ . These findings are of critical importance for the fabrication of future high mobility MOS transistors with GeSn channels.

This work has been partially supported by the LabEx MINOS ANR-10-LABX-55-01.

### **REFERENCES**

<sup>1</sup>R. Chen, H. Lin, Y. Huo, C. Hitzman, T. I. Kamins, and J. S. Harris, Appl. Phys. Lett. **99**, 181125 (2011).

<sup>2</sup>P. Moontragoon, Z. Ikonić, and P. Harrison, Semicond. Sci. Technol. 22, 742 (2007).

<sup>3</sup>J. D. Sau and M. L. Cohen, Phys. Rev. B 75, 045208 (2007).

<sup>4</sup>S. Wirths, D. Buca, G. Mussler, A. T. Tiedemann, B. Holländer, P. Bernardy, T. Stoica, D. Grützmacher, and S. Mantl, ECS J. Solid State Sci. Technol. **2**, N99 (2013).

<sup>5</sup>J. Aubin, J. M. Hartmann, A. Gassenq, J. L. Rouviere, E. Robin, V. Delaye, D. Cooper, N. Mollard, V. Reboud, and V. Calvo, Semicond. Sci. Technol. 32, 094006 (2017).

<sup>6</sup>J. Aubin, J. M. Hartmann, J. P. Barnes, J. B. Pin, and M. Bauer, ECS J. Solid State Sci. Technol. 6, P21 (2017).

<sup>7</sup>G. Grzybowski, R. T. Beeler, L. Jiang, D. J. Smith, J. Kouvetakis, and J. Menéndez, Appl. Phys. Lett. 101, 072105 (2012).

<sup>8</sup>M. Oehme, K. Kostecki, M. Schmid, F. Oliveira, E. Kasper, and J. Schulze, Thin Solid Films 557, 169 (2014).

- <sup>9</sup>N. Taoka, G. Capellini, N. Von Den Driesch, D. Buca, P. Zaumseil, M. A. Schubert, W. M. Klesse, M. Montanari, and T. Schroeder, Appl. Phys. Express

- <sup>10</sup>Y. Liu, J. Yan, H. Wang, Q. Zhang, M. Liu, B. Zhao, C. Zhang, B. Cheng, Y. Hao, and G. Han, IEEE Trans. Electron Devices 61, 3639 (2014).

- <sup>11</sup>G. Han, S. Su, Y. Yang, P. Guo, X. Gong, L. Wang, W. Wang, C. Guo, G. Zhang, C. Xue, B. Cheng, and Y. C. Yeo, ECS Trans. 50, 943 (2013).

- <sup>12</sup>T. Maeda, W. Jevasuwan, H. Hattori, N. Uchida, S. Miura, and M. Tanaka, Jpn. J. Appl. Phys., Part 1 54, 04DA07 (2015).

- 13 T. H. Liu, P. Y. Chiu, Y. Chuang, C. Y. Liu, C. H. Shen, G. L. Luo, and J. Y. Li, IEEE Electron Device Lett. 39, 468 (2018).

- <sup>14</sup>S. Gupta, B. Vincent, B. Yang, D. Lin, F. Gencarelli, J. Y. J. Lin, R. Chen, O. Richard, H. Bender, B. Magyari-Kope, M. Caymax, J. Dekoster, Y. Nishi, and K. C. Saraswat, in IEEE IEDM Technical Digest (2012), p. 375.

- 15Y. Yang, S. Su, P. Guo, W. Wang, X. Gong, L. Wang, K. L. Low, G. Zhang, C. Xue, B. Cheng, G. Han, and Y.-C. Yeo, in Proceedings of the International Electron Devices Meeting (IEEE, 2012), pp. 16.3.1-16.3.4.

- 16G. Han, Y. Wang, Y. Liu, C. Zhang, Q. Feng, M. Liu, S. Zhao, B. Cheng, J. Zhang, and Y. Hao, IEEE Electron Device Lett. 37, 6 (2016).

- <sup>17</sup>E. G. Rolseth, A. Blech, I. A. Fischer, Y. Hashad, R. Koerner, K. Kostecki, A. Kruglov, V. S. S. Srinivasan, M. Weiser, T. Wendav, K. Busch, and J. Schulze, "Device performance tuning of Ge gate-all-around tunneling field effect transistors by means of GeSn: Potential and challenges," 40th International Convention on Information and Communication Technology, Electronics and Microelectronics (IEEE, 2017), pp. 57.

- <sup>18</sup>C. Schulte-Braucks, R. Pandey, R. N. Sajjad, M. Barth, R. K. Ghosh, B. Grisafe, P. Sharma, N. Von Den Driesch, A. Vohra, G. B. Rayner, R. Loo, S. Mantl, D. Buca, C. C. Yeh, C. H. Wu, W. Tsai, D. A. Antoniadis, and S. Datta, IEEE Trans. Electron Devices 64, 4354 (2017).

- <sup>19</sup>X. Gong, G. Han, B. Liu, L. Wang, W. Wang, Y. Yang, E. Y.-J. Kong, S. Su, C. Xue, B. Cheng, and Y.-C. Yeo, IEEE Trans. Electron Devices 60, 1640 (2013).

- <sup>20</sup>M. A. Mahjoub, T. Haffner, S. Labau, E. Eustache, J. Aubin, J.-M. Hartmann, G. Ghibaudo, B. Pelissier, F. Bassani, and B. Salem, ACS Appl. Electron. Mater. 1, 260 (2019).

- <sup>21</sup>S. Wirths, D. Stange, M. A. Pampillón, A. T. Tiedemann, G. Mussler, A. Fox, U. Breuer, B. Baert, E. San Andrés, N. D. Nguyen, J. M. Hartmann, Z. Ikonic, S. Mantl, and D. Buca, ACS Appl. Mater. Interfaces 7, 62 (2015).

- <sup>22</sup>E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology (Wiley, 2002).

- <sup>23</sup>X. Liu, J. Xu, L. Liu, Z. Cheng, Y. Huang, and J. Gong, J. Semicond. 38, 1 (2017).

- **24**Y. Q. Cao, J. Chen, X. J. Liu, X. Li, Z. Y. Cao, Y. J. Ma, D. Wu, and A. D. Li, Appl. Surf. Sci. 325, 13 (2015).

- <sup>25</sup>Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J.

- W. Rodwell, and Y. Taur, IEEE Electron Device Lett. 32, 485 (2011).

- <sup>26</sup>E. H. Nicollian and A. Goetzberger, Bell Syst. Tech. J. **46**(6), 1055–1133 (1967). <sup>27</sup>C. Schulte-Braucks, K. Narimani, S. Glass, N. von den Driesch, J. M. Hartmann, Z. Ikonic, V. V. Afanas'ev, Q. T. Zhao, S. Mantl, and D. Buca, ACS Appl. Mater. Interfaces 9(10), 9102 (2017).

- <sup>28</sup>H. B. Michaelson, J. Appl. Phys. **48**, 4729 (1977).

- <sup>29</sup>S. Gupta, E. Simoen, R. Loo, O. Madia, D. Lin, C. Merckling, Y. Shimura, T. Conard, J. Lauwaert, H. Vrielinck, and M. Heyns, ACS Appl. Mater. Interfaces 8, 13181 (2016).

- 30W. S. M. Werner, G. C. Smith, and A. K. Livesey, Surf. Interface Anal. 21, 38

- 31R. P. Vasquez, J. D. Klein, J. J. Barton, and F. J. Grunthaner, J. Electron. pectrosc. Relat. Phenom. 23, 63 (1981).

- 32W. P. Bai, N. Lu, J. Liu, A. Ramirez, D. L. Kwong, D. Wristers, A. Ritenour, L. Lee, and D. Antoniadis, in Proceedings of the IEEE Symposium on VLSI Technology Technical Digest (Japan Society of Applied Physics, 2015), IEEE Cat. No. 03CH37407, pp. 121-122.

- 33Y. Kamata, Y. Kamimuta, T. Ino, and A. Nishiyama, Jpn. J. Appl. Phys., Part 1 44, 2323 (2005).

- 34E. Martinez, E. Nolot, J.-P. Barnes, Y. Mazel, N. Bernier, R. Muthinti, H. Jagannathan, C. Lee, and N. Gambacorti, J. Vac. Sci. Technol. B 36, 042902

- 35N. Lu, W. Bai, A. Ramirez, C. Mouli, A. Ritenour, M. L. Lee, D. Antoniadis, and D. L. Kwong, Appl. Phys. Lett. 87, 051922 (2005).