# Impact of Post-Deposition Anneal on ALD Al2O3/etched GaN Interface for Gate-First MOSc-HEMT

Paes Fernandes Paes Pinto Rocha, L. Vauche, B. Mohamad, W. Vandendaele, E. Martinez, M. Veillerot, T. Spelta, N. Rochat, R. Gwoziecki, B. Salem, et al.

## ▶ To cite this version:

Paes Fernandes Paes Pinto Rocha, L. Vauche, B. Mohamad, W. Vandendaele, E. Martinez, et al.. Impact of Post-Deposition Anneal on ALD Al2O3/etched GaN Interface for Gate-First MOSc-HEMT. Power Electronic Devices and Components, 2023, pp.100033. 10.1016/j.pedc.2023.100033. hal-03940756

# HAL Id: hal-03940756 https://cnrs.hal.science/hal-03940756

Submitted on 16 Jan 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Impact of Post-Deposition Anneal on ALD Al<sub>2</sub>O<sub>3</sub>/etched GaN Interface for Gate-First MOSc-HEMT

P. Fernandes Paes Pinto Rocha, L. Vauche, B. Mohamad, W. Vandendaele, E. Martinez, M. Veillerot, T. Spelta, N. Rochat, R. Gwoziecki, B. Salem, V. Sousa

PII: S2772-3704(23)00001-9

DOI: https://doi.org/10.1016/j.pedc.2023.100033

Reference: PEDC 100033

To appear in: Power Electronic Devices and Components

Received date: 18 June 2022

Revised date: 16 December 2022

Accepted date: 12 January 2023

Please cite this article as: P. Fernandes Paes Pinto Rocha, L. Vauche, B. Mohamad, W. Vandendaele, E. Martinez, M. Veillerot, T. Spelta, N. Rochat, R. Gwoziecki, B. Salem, V. Sousa, Impact of Post-Deposition Anneal on ALD Al<sub>2</sub>O<sub>3</sub>/etched GaN Interface for Gate-First MOSc-HEMT, *Power Electronic Devices and Components* (2023), doi: https://doi.org/10.1016/j.pedc.2023.100033

This is a PDF file of an article that has undergone enhancements after acceptance, such as the addition of a cover page and metadata, and formatting for readability, but it is not yet the definitive version of record. This version will undergo additional copyediting, typesetting and review before it is published in its final form, but we are providing this version to give early visibility of the article. Please note that, during the production process, errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

© 2023 Published by Elsevier Ltd.

This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

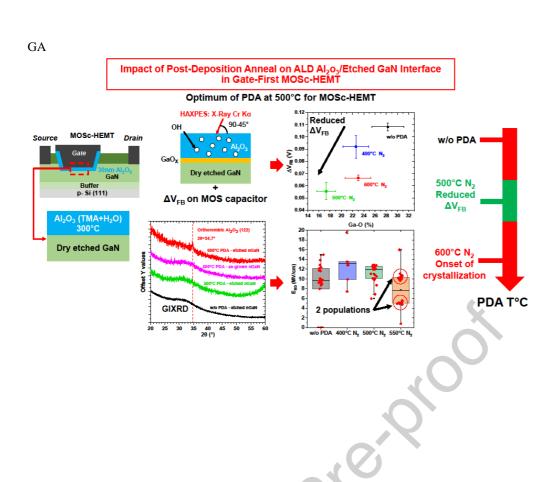

### Highligths

- Under 500°C in PDA, Flat band voltage hysteresis (ΔV<sub>FB</sub>) is reduced in accordance with the reduction of GaO<sub>X</sub> and OH groups

- Over 500°C in PDA,  $\Delta V_{FB}$  increases, due to the increase of GaOx

- The Fluorine reduction with increasing PDA temperature could explained the decrease of Flat-band Voltage (V<sub>FB</sub>)

- Al<sub>2</sub>O<sub>3</sub> on etched GaN substrate crystallizes for a PDA over 500°C leading to degraded breakdown field

# Impact of Post-Deposition Anneal on ALD Al<sub>2</sub>O<sub>3</sub>/etched GaN Interface for Gate-First MOSc-HEMT

P. Fernandes Paes Pinto Rocha<sup>1,2</sup>, L. Vauche<sup>1</sup>, B. Mohamad<sup>1</sup>, W. Vandendaele<sup>1</sup>, E. Martinez<sup>1</sup>, M. Veillerot<sup>1</sup>, T. Spelta<sup>1</sup>, N. Rochat<sup>1</sup>, R. Gwoziecki<sup>1</sup>, B. Salem<sup>2</sup>, V. Sousa<sup>1</sup>

#### **Affiliations:**

- (1) Univ. Grenoble Alpes, CEA, Leti, F-38000 Grenoble, France

- (2) Univ. Grenoble Alpes, CNRS, CEA/ LETI Minatec, Grenoble INP, LTM, F-38054 Grenoble, France

### **Corresponding Author:**

E-mail address: <a href="mailto:pedro.fernandespaespintorocha@cea.fr">pedro.fernandespaespintorocha@cea.fr</a> (P. Fernandes Paes Pinto Rocha)

Abstract— MOS High Electron Mobility Transistors (MOS-HEMTs) may suffer from  $V_{TH}$  instability and hysteresis reducing device performances. Post-Deposition Anneal (PDA) of the Atomic-Layer Deposited (ALD) dielectric has the potential to increase MOS-HEMT performances but needs to be compatible with the actual integration (at CEA Leti: fully recessed Gate First MOS-channel HEMT process flow). In this work, the impact of different PDA temperatures on flat-band voltage ( $V_{FB}$ ) and its hysteresis ( $\Delta V_{FB}$ ) for  $Al_2O_3$  deposited on etched GaN substrates is investigated using MOS capacitors (MOSCAPs). Material properties are analyzed by Hard X-Ray Photoelectron Spectroscopy (HAXPES), Fourier transform infrared spectroscopy (FTIR) and Time-of-Flight Secondary Ion Mass Spectrometry (ToF-SIMS) analyses. With increasing PDA temperature up to  $500^{\circ}$ C: (i)  $\Delta V_{FB}$  decreases and is explained by the reduction of Ga-O bonds at  $Al_2O_3$ /GaN interface and O-H groups in  $Al_2O_3$  (ii)  $V_{FB}$  decreases and could be explained by the reduction of fluorine impurity concentration in  $Al_2O_3$ . For  $600^{\circ}$ C PDA, Grazing Incidence X-Ray Diffraction (GIXRD) analysis shows a small crystallized  $\kappa$ - $Al_2O_3$  signal on etched GaN contrary to the as-grown GaN. The onset of this crystallization could explain the degradation in breakdown field for PDA above  $500^{\circ}$ C observed on MOSCAPs after the Gate-First process flow overall thermal budget. Therefore, the optimized PDA temperature suggested for a fully recessed Gate First MOSchannel HEMT is  $500^{\circ}$ C.

KEYWORDS: Post-Deposition Anneal, Al<sub>2</sub>O<sub>3</sub>, GaN, MOS, ALD, Hard X-Ray photoelectron spectroscopy

ABBREVIATIONS: MOS-channel High Electron Mobility Transistors (MOSc-HEMTs), Hard X-Ray photoelectron spectroscopy (HAXPES), Fourier transform infrared spectroscopy (FTIR), Time-of-Flight Secondary Ion Mass Spectrometry (ToF-SIMS), Grazing Incidence X-Ray Diffraction (GIXRD)

#### 1. Introduction

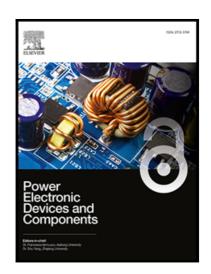

Due to their two-dimensional electron gas (2DEG) obtained from AlGaN/GaN heterojunction, GaN based high electron mobility transistors (HEMTs) are interesting for the field of power electronics where higher switching frequency and reduced on-state-resistance ( $R_{on}$ ) [1] are required. HEMTs are normally-on devices with a negative threshold voltage ( $V_{TH}$ <0). However, for safety issues and simplified driver systems design, HEMTs with a positive threshold voltage addressed as "normally-off" are highly demanded. One approach is the partial recess of the AlGaN barrier, increasing  $V_{TH}$  by reducing the 2DEG, but with the drawback of having a  $V_{TH}$  sensible to small variations in the recess depth. To overcome this issue, the MOS-channel HEMT (MOSc-HEMT) with its fully recessed AlGaN barrier and MOS gate (**Fig. 1**) totally depletes the 2DEG assuring a positive  $V_{TH}$ , and reduces the gate current leakage [2]. Still, its  $V_{TH}$  depends on the gate dielectric  $Al_2O_3$ /etched GaN interface properties [3]. Post-Deposition Anneal (PDA) of  $Al_2O_3$ /GaN has been reported to increase the threshold voltage and reduce its hysteresis ( $\Delta V_{TH}$ ) [4], [5]. Except for Kim et al. [6], most of these reports are for  $Al_2O_3$  deposited either on as-grown or etched GaN substrates using a Gate-Last process flow in which the source and the drain fabrication is carried before the gate fabrication. Since our MOSc-HEMT process flow is Gate-First with a final thermal budget including ohmic contact annealing [7], the impact of  $Al_2O_3$  PDA deposited on etched GaN for the Gate-First process flow is investigated with electrical and chemical characterizations.

#### 2. MATERIALS AND METHODS

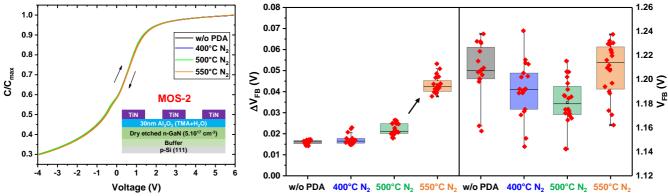

In order to reproduce the MOSc-HEMT gate processing, 30nm of  $Al_2O_3$  was deposited by Atomic Layer Deposition (ALD) at  $300^{\circ}$ C using TMA and  $H_2O$  precursors on dry etched nGaN/Si wafers. The 200nm nGaN/Si wafers were grown using Metal Organic Chemical Vapor Deposition (MOCVD) on Si substrates, with an GaN n-type doping of  $5.10^{17}$  cm<sup>-3</sup>. The dry etching was performed using Inductively Coupled Plasma Reactive Ion Etching (ICP-RIE) with chlorine-based chemistry. A wet cleaning containing HF was carried out before  $Al_2O_3$  deposition. Since minor consensus is found for PDA's duration, with duration ranging from 30s to 90min [8], [9], a low PDA's duration is performed. Hence, after ALD, PDA was performed under  $N_2$  1) for 4 min at 400, 500, and  $600^{\circ}$ C on 1.5 cm  $\times$  1.5 cm samples or 2) for 5 min at 400, 500, and  $550^{\circ}$ C on 200mm wafers. MOSCAPs test structures were then fabricated: 1) on the 1.5 cm  $\times$  1.5 cm samples with Au/Ni metal contacts deposited by e-beam evaporation (MOS-1) and 2) on the 200 mm wafers with TiN metal contacts deposited by Physical Vapor Deposition (MOS-2). The MOS-2 devices were annealed after metal deposition to simulate the Gate-First thermal budget including a rapid thermal annealing which was in the temperature range of 400- $650^{\circ}$ C. The process flows for the two devices are summarized in Fig. 1.

Fig. 1: On the left, the schematic representation of a MOSc-HEMT. On the right, the schematic representation and process flows for MOS-1 and MOS-2

C-V measurements were performed at 1 kHz with a forward voltage sweep from -4V to 6V and backward to -4V using an Agilent 4284A for MOS-1 and using an Agilent B1505A for MOS-2 devices. The flat-band voltage  $(V_{FB})$  was extracted using the theoretical flat-band capacitance, which is:

$$C_{FB} = C_{OX}C_D/(C_{OX} + C_D)$$

with  $C_D = \sqrt{kT\varepsilon_{GaN}\varepsilon_0/(q^2N_D)}$

where  $C_{ox}$ , k, T,  $\varepsilon_{GaN}$ ,  $\varepsilon_0$  and q are respectively the oxide capacitance, the Boltzmann constant, the temperature in Kelvin, the relative GaN permittivity, the vacuum permittivity and the electron elementary charge. The hysteresis ( $\Delta V_{FB}$ ) is defined as the difference between  $V_{FB}$  in reverse and forward sweeps. Current density-Voltage (J-V) measurements were performed using an Agilent B1505A for MOS-2.

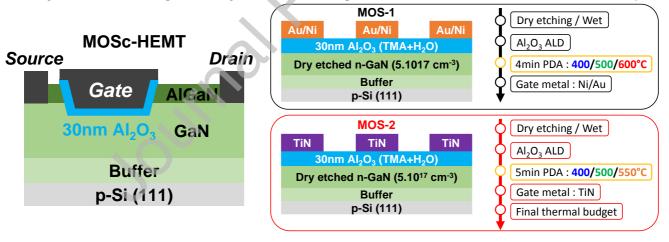

For physical and chemical characterizations, specific Al<sub>2</sub>O<sub>3</sub>/GaN samples were prepared with the same processing conditions but with only 15nm of Al<sub>2</sub>O<sub>3</sub>. The PDA conditions were the same as for MOS-1 devices. Hard X-Ray Photoelectron

Spectroscopy (HAXPES), Time-of-Flight Secondary Ion Mass Spectrometry (ToF-SIMS) and Grazing Incidence X-Ray Diffraction (GIXRD) were performed on these dedicated samples. HAXPES analyses were conducted on a PHI Quantes, equipped with both monochromatic Al K $\alpha$  (hv=1486.7 eV) and Cr K $\alpha$  (hv=5414.7eV) X-Ray sources, the last one allowing the analysis of buried interfaces. Since the C1s intensity is strongly reduced with a Cr K $\alpha$  source, the binding energy was calibrated with the O1s peak (531.2eV), as measured using the Al K $\alpha$  source and referenced to the C1s peak (284.8eV). The photoelectron take-off angles were set at 45° (Ga2p<sub>3/2</sub>) and 90° (O1s) respectively, yielding integrated sampling depths of approximately 16.6 and 24 nm with the Cr K $\alpha$  source. As seen in **Fig. 2a**, three contributions for Ga2p<sub>3/2</sub> were used: Ga-N (~1117.8eV), Ga-O (~1118.4eV) and Ga-Ga (~1116.5eV). In order to have a comparable analysis, the energy shifts of Ga-O and Ga-Ga with respect to Ga-N were fixed at 0.7eV [10] and -1.3eV [11] respectively. GaN oxidation at the interface was analyzed with the Ga-O area percentage in Ga2p<sub>3/2</sub> peak. Similarly, O1s peaks were analyzed using O-Al (~531eV) and O-H (~532.2eV) contributions, the energy shift between O-H and O-Al being fixed to 1.2eV [12]. The O1s spectrum with the associated peak fitting is shown in **Fig. 2b**. As for gallium oxide, the presence of O-H groups was deduced from the area of O-H bonds in O1s peak.

Fig. 2: a) Ga2p<sub>3/2</sub> spectrum from the reference with a take-off angle of 45°; b) O1s spectrum from the reference with a take-off angle of 90°

ToF-SIMS analyses were performed using a 500eV Cs<sup>+</sup> sputter gun and by detecting negative secondary ions. GIXRD was performed with a 2° incident angle and  $2\theta$  angle between  $20^\circ$  and  $60^\circ$ . Finally, for Fourier transform infrared spectroscopy (FTIR) with multiple internal reflection, dedicated  $Al_2O_3/Si$  samples of 30nm  $Al_2O_3$  deposited by ALD on p-Si samples were analyzed to study the impact of PDA on OH groups. A manual baseline correction was performed.

#### 3. RESULTS AND DISCUSSION

#### 3.1. PDA without final thermal budget

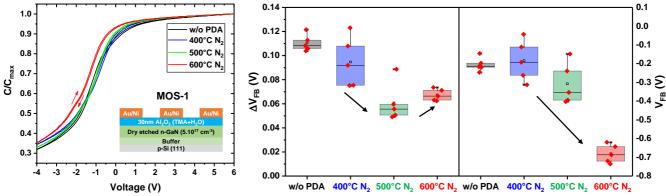

The C-V measurements for MOS-1 devices are reported in **Fig. 3**, with  $\Delta V_{FB}$  and  $V_{FB}$  being extracted and shown in **Fig. 4**.  $\Delta V_{FB}$  is reduced with increasing PDA temperature until a minimum at 500°C, reducing from 108mV to 56mV between the reference and the PDA at 500°C. The reduction of  $\Delta V_{FB}$  with PDA temperature was similarly observed in previous reports [4], [5], [13]. However, for a PDA over 500°C, an increase of  $\Delta V_{FB}$  is observed.

Fig. 3: Normalized C-V characteristics at 1 kHz for MOS-1 devices (median of five measurements)

Fig. 4:  $\Delta V_{FB}$  and  $V_{FB}$  for MOS-1 devices extracted from C-V measurements

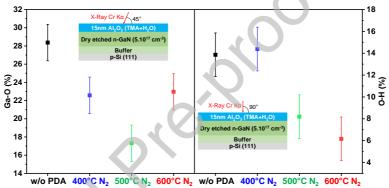

In the same way, Ga-O bonds observed by HAXPES and related to the presence of interfacial gallium oxide  $(GaO_X)$  reduce with PDA temperature until 500°C and increase over 500°C (**Fig. 5**). Since the  $GaO_X$  reduction was reported to reduce hysteresis [14], [15], the reduction of hysteresis with PDA temperature is attributed to  $GaO_X$  reduction at the  $Al_2O_3/GaN$  interface.

Fig. 5: HAXPES extracted chemical environments (Ga-O and O-H bonds) for different PDA temperatures and without final thermal budget. The take-off angle was  $45^{\circ}$  for Ga  $2p_{3/2}$  and  $90^{\circ}$  for O1s analysis.

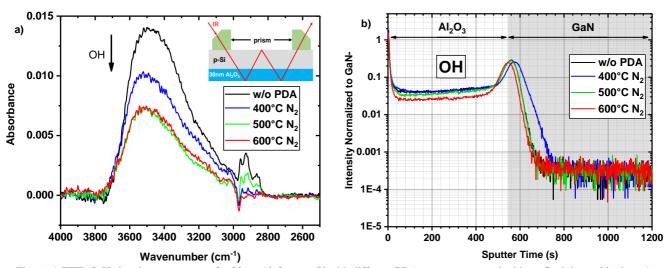

Likewise, OH groups' reduction is observed in  $Al_2O_3$  with increasing PDA temperature. Indeed, OH reduction is confirmed by HAXPES analyses (**Fig. 5**), as also previously observed by Zhu et al. [16] but with standard XPS. This reduction is also confirmed both by FTIR and ToF-SIMS analyses (**Fig. 6**). With FTIR, the absorbance spectrum associated to OH bonds reduces and reaches a minimum at  $500^{\circ}$ C. Through ToF-SIMS, the OH reduction is seen to occur mainly in  $Al_2O_3$  bulk, little reduction at the interface being observed. Specifically, the stretch of OH profile in the GaN substrate for  $400^{\circ}$ C was also observed for other elements from  $Al_2O_3$  and could be attributed to the impact of surface roughness. Similarly to  $Al_2O_3$ , the reduction of OH groups was associated with a reduction of hysteresis [14]. As a matter of fact, interstitial hydrogen defect energy levels in amorphous  $Al_2O_3$  were reported to be close to GaN conduction band [17]. This proximity to the conduction band can lead to electron trapping, root cause of the hysteresis. Hence, both reducing OH groups and  $Al_2O_3$  with increasing PDA temperature until  $Al_2O_3$  reduce the hysteresis.

Fig. 6: a) FTIR O-H absorbance spectrum for 30nm  $Al_2O_3$  on p-Si with different PDA temperatures and without final thermal budget. A manual correction of base line was performed; b) OH profiles by ToF-SIMS for different PDA temperatures

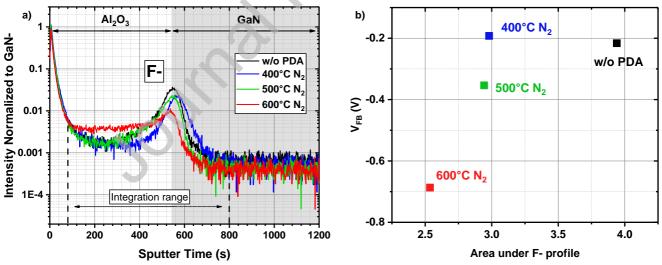

A small reduction of  $V_{FB}$  up to 500°C and a strong decrease for a PDA over 500°C is noticed for MOS-1 devices, going from -220mV to -350mV between the reference and the PDA at 500°C and down to -700mV for a PDA at 600°C (**Fig. 4**). The decrease of  $V_{FB}$  could be detrimental to our MOSc-HEMT, leading to a lower  $V_{TH}$ . The  $V_{FB}$  reduction seems to follow the trend of fluorine reduction at the interface observed by ToF-SIMS analyses as reported in **Fig. 7**. Indeed, fluorine profile at the interface reduces with the PDA temperature, with a strong decrease for 600°C. Likewise, the content of fluorine represented by the integrated area under fluorine profile reduces with PDA temperature. A diffusion of fluorine in  $Al_2O_3$  bulk region is also observed for a PDA higher than 500°C. As for OH groups, the stretch of fluorine in the GaN substrate for 400°C can be attributed to the surface roughness. The origin of fluorine contamination could be attributed to the wet cleaning containing HF [18]. Since fluorine doping of  $Al_2O_3$  is also used to increase  $V_{TH}$  by introducing negative charges [19], [20], the reduction of fluorine could explain the reduction of  $V_{FB}$  for MOS-1 devices. Nonetheless, the reduction of  $V_{FB}$  could also be explained by the increase of positives charges present such as  $V_0^{+2}$  or  $Al_1^{+3}$  or the decrease of negatives charges such as  $O_1^{-2}$  or  $V_{Al}^{-3}$ [21], [22].

Fig. 7: a) Fluorine profiles obtained by ToF-SIMS for different PDA temperatures; b) Integrated area under fluorine profiles for a defined range as a function of  $V_{FB}$  for MOS-1 devices.

Hence, without the final thermal budget, a PDA until 500° is beneficial to reduce  $\Delta V_{FB}$  and limit the reduction of  $V_{FB}$ . Further increasing the PDA temperature leads to an increased  $\Delta V_{FB}$  and reduced  $V_{FB}$ .

#### 3.2. PDA with the final thermal budget

In the case of MOS-2 devices having the final thermal budget, the CV measurements are reported in Fig. 8, with the extracted  $\Delta V_{FB}$  and  $V_{FB}$  shown in Fig. 9. The impact of different PDA temperatures is reduced, with  $\Delta V_{FB}$  being around 20mV for a PDA temperature lower than 500°C (Fig. 9). However, a PDA over 500°C induces an increase in hysteresis. On the other hand,  $V_{FB}$  is

around 1.2V for all PDA temperatures (**Fig. 9**). Considering that all MOS-2 samples were subject to the final thermal budget, the stable  $V_{FB}$  could be explained by an overall reduction of Fluorine.

Fig. 8: Normalized C-V characteristics at 1 kHz for MOS-2 devices (median of nineteen measurements)

Fig. 9:  $\Delta V_{FB}$  and  $V_{FB}$  for MOS-2 devices extracted from C-V measurements

The difference between MOS-1 and MOS-2 could be attributed to the impact of the final thermal budget. The  $V_{FB}$  is increased (from -0.2 to 1.2 V) and stabilized together with a reduction of  $\Delta V_{FB}$  for PDA under 500°C (from 0.11 to 0.02 V). Further investigation is needed to understand its impact. Indeed, the thermal budget can act as a Post-Metallization Anneal (PMA) on the gate properties, which has been reported to be beneficial [21], [23]. Another difference is the gate metal material and deposition technique, which can affect the  $V_{FB}$ . Indeed, e-beam evaporation was reported to introduce positive charges [24] hence reducing  $V_{FB}$  for MOS-1 devices.

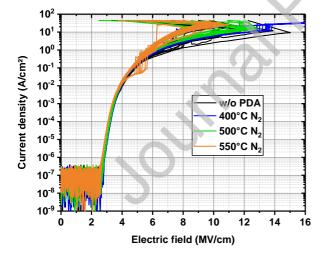

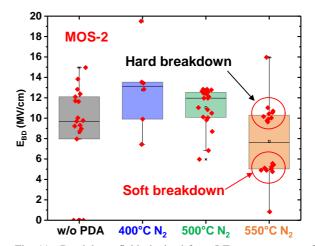

Moreover, the breakdown field extracted from J-E measurements for MOS-2 devices (**Fig. 10**) is degraded when the PDA temperature is above 500°C, with early breakdown for a given population of devices at 550°C (Error! Reference source not found.). The early breakdown is associated to soft breakdown mechanism whereas the higher breakdown is related to the hard breakdown.

Fig. 11 : Breakdown field obtained from J-E measurements of MOS-2 devices after the final thermal budget.

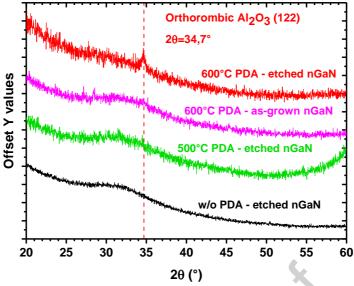

Furthermore, with GIXRD, the presence of an orthorhombic  $\kappa$ -Al<sub>2</sub>O<sub>3</sub> peak is observed for a PDA at 600°C and attributed to the (122) plan (**Fig. 12**). This indicates the beginning of crystallization for Al<sub>2</sub>O<sub>3</sub>. The absence of peaks with a PDA at 500°C for etched GaN substrates and with a PDA at 600°C for as-grown GaN substrates confirms that the crystallization onset occurs above 500°C for an etched GaN substrate. The crystallization temperature is lower than the temperature of 850°C reported for ALD Al<sub>2</sub>O<sub>3</sub> on etched GaN [6]. This difference could be ascribed to the different cleaning sequence (i.e. TMAH) and different oxidant precursor (i.e. O<sub>2</sub> plasma) as well as the etching process. The GaN etched surface is believed to be the reason for the reduced Al<sub>2</sub>O<sub>3</sub> crystallization onset temperature (~600°C), further consolidating the need for studies on etched substrates, with processing conditions as similar as possible as the actual transistor process flow.

Fig. 12 : GIXRD analysis with grazing angle of  $2^{\circ}$  for 15nm  $Al_2O_3$  on eached GaN without PDA, with a 500°C and 600°C PDA, and for 15nm  $Al_2O_3$  on as-grown GaN with a 600°C PDA. All the samples have no final thermal budget.

The observed beginning of crystallization above 500°C can explain the degradation of the breakdown field. Indeed, the formation of grain boundaries can act as current paths resulting to be detrimental for the breakdown field. This observation further consolidates the negative impact of PDA above 500°C for Al<sub>2</sub>O<sub>3</sub> deposited on etched GaN.

Hence, with the increased hysteresis and degraded breakdown field, the combination of PDA and final thermal annealing is detrimental in the case of PDA temperature over 500°C.

#### 4. CONCLUSION

The impact of PDA for  $Al_2O_3$  on etched GaN substrates for Gate-First MOSc-HEMTs process flow was investigated with both electrical and chemical characterizations. In the case of PDA below 500°C without the final thermal budget, the beneficial reduction of hysteresis is observed, correlated to the reduction of  $GaO_X$  at the  $Al_2O_3/GaN$  interface and OH groups in the alumina. A small reduction of  $V_{FB}$  following the trend of fluorine reduction in  $Al_2O_3$  is also observed. However, for a PDA above  $500^{\circ}C$ , the hysteresis increases likewise linked to the increase of  $GaO_X$ .

With the device final thermal budget, the PDA's effect on  $V_{FB}$  is reduced. However, the degradation of hysteresis is equally observed for a PDA over 500°C. Furthermore, a degradation of breakdown field is observed and is explained by the beginning of  $Al_2O_3$  crystallization appearing only on etched GaN substrates.

Therefore, the overall thermal budget and the GaN processing prior to  $Al_2O_3$  deposition, both influence the impact of PDA; these parameters should be taken into account when optimizing the PDA for the Gate-First approach. The best PDA conditions so far for our MOSc-HEMT architecture seem to be  $500^{\circ}$ C.

#### 5. Funding

This work was partially supported by the French Public Authorities within the frame of the PSPC French national program "G-Mobility", the French RENATECH network through the PTA technological platforms, and the "Recherches Technologiques de Base" program of the French National Research Agency (ANR) regarding the measurements done at the NanoCharacterization PlatForm (PFNC).

#### **Declaration of interests**

☑ The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### REFERENCES

- [1] J. He, W.-C. Cheng, Q. Wang, K. Cheng, H. Yu, and Y. Chai, "Recent Advances in GaN- Based Power HEMT Devices," *Advanced electronic materials*, vol. 7, no. 4, p. 2001045, 2021, doi: 10.1002/aelm.202001045.

- [2] T. Oka and T. Nozawa, "AlGaN/GaN Recessed MIS-Gate HFET With High-Threshold-Voltage Normally-Off Operation for Power Electronics Applications," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 668–670, Jul. 2008, doi: 10.1109/LED.2008.2000607.

- [3] L. Vauche *et al.*, "Study of an Al<sub>2</sub> O<sub>3</sub> /GaN Interface for Normally Off MOS-Channel High-Electron-Mobility Transistors Using XPS Characterization: The Impact of Wet Surface Treatment on Threshold Voltage Vth," *ACS Appl. Electron. Mater.*, vol. 3, no. 3, pp. 1170–1177, Mar. 2021, doi: 10.1021/acsaelm.0c01023.

- [4] Q. Zhou *et al.*, "7.6 V Threshold Voltage High-Performance Normally-Off Al<sub>2</sub> O<sub>3</sub> /GaN MOSFET Achieved by Interface Charge Engineering," *IEEE ELECTRON DEVICE LETTERS*, vol. 37, no. 2, p. 4, 2016, doi: 10.1109/LED.2015.2511026.

- [5] T. Kubo, M. Miyoshi, and T. Egawa, "Post-deposition annealing effects on the insulator/semiconductor interfaces of Al<sub>2</sub> O<sub>3</sub> /AlGaN/GaN structures on Si substrates," *Semicond. Sci. Technol.*, vol. 32, no. 6, p. 065012, Jun. 2017, doi: 10.1088/1361-6641/aa6c09.

- [6] K.-W. Kim et al., "Charge trapping and interface characteristics in normally-off Al<sub>2</sub> O<sub>3</sub> /GaN-MOSFETs," Microelectronic Engineering, vol. 88, no. 7, pp. 1225–1227, Jul. 2011, doi: 10.1016/j.mee.2011.03.116.

- [7] C. L. Royer et al., "Normally-OFF 650V GaN-on-Si MOSc-HEMT Transistor: Benefits of the Fully Recessed Gate Architecture," p. 3.

- [8] T. L. Duan, J. S. Pan, and D. S. Ang, "Effect of Post-Deposition Annealing on the Interface Electronic Structures of Al<sub>2</sub> O<sub>3</sub> -Capped GaN and GaN/AlGaN/GaN Heterostructure," ECS J. Solid State Sci. Technol., vol. 4, no. 9, pp. P364–P368, 2015, doi: 10.1149/2.0081509jss.

- [9] S. Nakazawa *et al.*, "Effects of post-deposition annealing in O2 on threshold voltage of Al<sub>2</sub> O<sub>3</sub> /AlGaN/GaN MOS heterojunction field-effect transistors," *Jpn. J. Appl. Phys.*, vol. 58, no. 3, p. 030902, Mar. 2019, doi: 10.7567/1347-4065/aafd17.

- [10] O. Renault et al., "New directions in the analysis of buried interfaces for device technology by hard X-ray photoemission," Faraday Discuss., p. 10.1039.D1FD00110H, 2022, doi: 10.1039/D1FD00110H.

- [11] Y. Fujimoto, M. Uenuma, T. Nakamura, M. Furukawa, Y. Ishikawa, and Y. Uraoka, "Physical and electrical properties of ALD-Al<sub>2</sub> O<sub>3</sub> /GaN MOS capacitor annealed with high pressure water vapor," *Jpn. J. Appl. Phys.*, vol. 58, no. 4, p. 040902, Apr. 2019, doi: 10.7567/1347-4065/ab09a2.

- [12] A. Abidli, S. Hamoudi, and K. Belkacemi, "Synthesis, characterization and insights into stable and well organized hexagonal mesoporous zinc-doped alumina as promising metathesis catalysts carrier," *Dalton Trans.*, vol. 44, no. 21, pp. 9823–9838, 2015, doi: 10.1039/C4DT03630A.

- [13] M. Ťapajna et al., "Investigation of 'surface donors' in Al<sub>2</sub> O<sub>3</sub> /AlGaN/GaN metal-oxide-semiconductor heterostructures: Correlation of electrical, structural, and chemical properties," Applied Surface Science, vol. 426, pp. 656–661, Dec. 2017, doi: 10.1016/j.apsusc.2017.07.195.

- [14] S. Ozaki et al., "Effect of Oxidant Source on Threshold Voltage Shift of AlGaN / GaN MIS-HEMTs Using ALD-Al<sub>2</sub> O<sub>3</sub> Gate Insulator films," presented at the CS MANTECH 2012 conference, Boston MA, 2011.

- [15] S. Yang et al., "High-Quality Interface in Al<sub>2</sub> O<sub>3</sub> /GaN/ AlGaN/GaN MIS Structures With In Situ Pre-Gate Plasma Nitridation," *IEEE Electron Device Lett.*, vol. 34, no. 12, pp. 1497–1499, Dec. 2013, doi: 10.1109/LED.2013.2286090.

- [16] L. Q. Zhu, Y. H. Liu, H. L. Zhang, H. Xiao, and L. Q. Guo, "Atomic layer deposited Al<sub>2</sub> O<sub>3</sub> films for anti-reflectance and surface passivation applications," *Applied Surface Science*, vol. 288, pp. 430–434, Jan. 2014, doi: 10.1016/j.apsusc.2013.10.051.

- [17] Z. Guo, F. Ambrosio, and A. Pasquarello, "Extrinsic Defects in Amorphous Oxides: Hydrogen, Carbon, and Nitrogen Impurities in Alumina," *Phys. Rev. Applied*, vol. 11, no. 2, p. 024040, Feb. 2019, doi: 10.1103/PhysRevApplied.11.024040.

- [18] S. Jakschik et al., "Physical characterization of thin ALD-Al<sub>2</sub> O<sub>3</sub> films," Applied Surface Science, vol. 211, no. 1–4, pp. 352–359, Apr. 2003, doi: 10.1016/S0169-4332(03)00264-2.

- [19] C. Chen *et al.*, "Fabrication of Enhancement-Mode AlGaN/GaN MISHEMTs by Using Fluorinated Al<sub>2</sub> O<sub>3</sub> as Gate Dielectrics," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1373–1375, Oct. 2011, doi: 10.1109/LED.2011.2162933.

- [20] J. W. Roberts et al., "Control of threshold voltage in E-mode and D-mode GaN-on-Si metal-insulator-semiconductor heterostructure field effect transistors by in-situ fluorine doping of atomic layer deposition Al<sub>2</sub> O<sub>3</sub> gate dielectrics," Appl. Phys. Lett., vol. 108, no. 7, p. 072901, Feb. 2016, doi: 10.1063/1.4942093.

- [21] T.-H. Hung, S. Krishnamoorthy, M. Esposto, D. Neelim Nath, P. Sung Park, and S. Rajan, "Interface charge engineering at atomic layer deposited dielectric/III-nitride interfaces," *Appl. Phys. Lett.*, vol. 102, no. 7, p. 072105, Feb. 2013, doi: 10.1063/1.4793483.

- [22] O. A. Dicks, J. Cottom, A. L. Shluger, and V. V. Afanas'ev, "The origin of negative charging in amorphous Al<sub>2</sub> O<sub>3</sub> films: the role of native defects," *Nanotechnology*, vol. 30, no. 20, p. 205201, May 2019, doi: 10.1088/1361-6528/ab0450.

- [23] K. Yuge, "Characteristics of Al<sub>2</sub> O<sub>3</sub> /native oxide/n-GaN capacitors by post-metallization annealing," Semicond. Sci. Technol., p. 8, 2019.

- [24] Y. Ando *et al.*, "Impact of gate electrode formation process on Al<sub>2</sub> O<sub>3</sub> /GaN interface properties and channel mobility," *Appl. Phys. Express*, vol. 14, no. 8, p. 081001, Aug. 2021, doi: 10.35848/1882-0786/ac0ffa.