## Experimental Study of Self-Heating Effect in InGaAs HEMTs for Quantum Technologies Down to 10K

F. Serra Di Santa Maria, C. B. Zota, E. Cha, Francis Balestra, C. Theodorou, G. Ghibaudo

#### ▶ To cite this version:

F. Serra Di Santa Maria, C. B. Zota, E. Cha, Francis Balestra, C. Theodorou, et al.. Experimental Study of Self-Heating Effect in InGaAs HEMTs for Quantum Technologies Down to 10K. IEEE International Reliability Physics Symposium (IRPS), Mar 2023, Monterey, United States. 10.1109/IRPS48203.2023.10118294. hal-04246081

### HAL Id: hal-04246081 https://cnrs.hal.science/hal-04246081v1

Submitted on 15 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Experimental Study of Self-Heating Effect in InGaAs HEMTs for Quantum Technologies Down to 10K

F. Serra di Santa Maria<sup>1</sup>, C. B. Zota<sup>2</sup>, E. Cha<sup>2</sup>, F. Balestra<sup>1</sup>, C. Theodorou<sup>1</sup>, G. Ghibaudo<sup>1</sup>

<sup>1</sup>Univ. Grenoble Alpes, Univ. Savoie Mont Blanc, CNRS, Grenoble INP, IMEP-LAHC, Grenoble, 38000, France <sup>2</sup>IBM Research GmbH Zürich Laboratory, Säumerstrasse 4, CH-8803 Rüschlikon, Switzerland

Abstract—This work studies self-heating effects in InGaAs cryogenic HEMT devices, which aim at the enhancement of control/readout electronics performance in quantum computers. Starting from the well-known method of gate resistance thermometry, documented in literature for its reliable results, we characterized these devices down to deep cryogenic temperatures, namely 10 K, typical of signal-processing electronics for qubits, such as low-noise amplifiers (LNA). We furthermore compared the results with those belonging to far more industrialized silicon technologies (Si FDSOI and bulk), showing exceptional performance of the InGaAs HEMTs thanks to their quantum well structure, which combined with their high electron-mobility, makes them a great study case for the technologies of the future.

Keywords - Self-Heating, HEMT, InGaAs, III-V, cryogenics, LNA, characterization

#### I. INTRODUCTION

Recently, interest in Quantum Computing (QC) has significantly increased. On one side, there are many efforts in developing new and more refined technologies for the actual qubits. On the other, there is also rising interest in integrating cryogenic electronics to enhance the scalability and performance of the QC. When considering the nature of QC and its architecture [1], we have to remember that some qubit technologies operate well below 1K and have a very low output signal power which needs to be amplified before going to higher temperatures and being digitized.

III-V-based high electron-mobility transistors (HEMTs) are proving great candidates for cryogenic LNA [2]; though in order enhance their performance for future scaled QCs, their characteristics have to be thoroughly investigated down to deep cryogenic temperatures. Particularly, self-heating represents an issue that not only interferes with low-temperature-induced boost in performances but also one that gives rise to the thermal noise in the amplifier, distorting the signal from the qubit before it can be processed.

Several studies have already been carried out on self-heating, more thoroughly for Silicon (Si) devices and with an increasing interest for III-V. Particularly, Choi et al. have characterized InGaAs-based HEMTs down to 20 K [3], while Ardizzi et al. have studied GaAs HEMTs down to liquid helium temperatures analyzing the noise temperature [4]. This work will instead study InGaAs-based HEMTs down to 10 K, showing their capacity to dissipate heat and stay in line with their ambient temperature, benchmarking them moreover with well-documented Si CMOS.

#### II. DEVICES AND METHODS

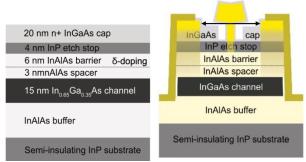

The devices under study were fabricated by IBM Research - Zurich and consist of an  $In_{0.53}Ga_{0.47}As$  channel, stacked inbetween two layers of InAlAs, as shown in Fig. 1. The InAlAs serves at the bottom as a buffer connecting to a semi-insulating InP substrate, and at the top as a spacer separating the channel from the delta-doping plane, and a third layer of InAlAs, to reduce possible gate leakages (Fig.1). For the present study, we tested single channel devices with channel width of 10  $\mu$ m and

channel length spanning from 50 nm up to 200 nm. In all cases, the distance between source and drain regions was  $1.4~\mu m$ .

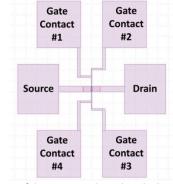

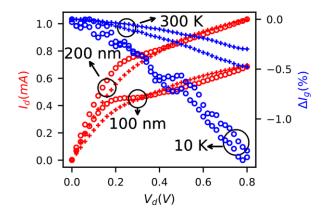

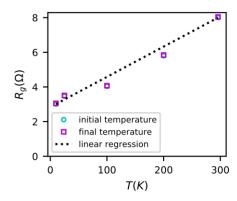

As shown by Paliwoda et al., many methods have been developed to assess self-heating [5]. One of the most reliable methods is gate thermometry, which relies on 4-terminal gate resistance measurements using a custom test structure (Fig. 2). As explained in [6] and [7], the increasing temperature in the channel causes an instantaneous heating of the gate metal which is measured through the change of the gate resistance. Thus, we performed gate resistance thermometry measurements by recording the current flowing between two metallic pads connected to the gate and biased with a small differential voltage  $\Delta V_g$  of 30 mV. As the drain voltage,  $V_d$ , increases and we move towards saturation region, the current  $\Delta I_g$  flowing between the gate pads decreases due to an increase in resistance, caused by the self-heating of the device (Fig. 3). As we extract the gate's metal pad resistance  $R_g$  (Eq. 1) in between the pads at the beginning  $(V_d = 0 \text{ V})$  and the end of each measurement (Fig. 4), we can compute the temperature variation  $\Delta T$  (Eq. 2), after linear regression of  $R_g(T)$ .

#### III. RESULTS AND DISCUSSION

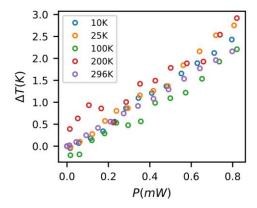

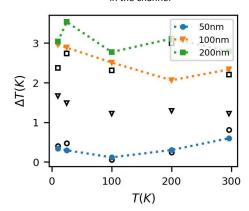

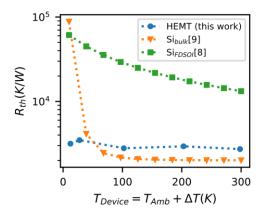

By following the aforementioned steps, we account for the self-heating  $\Delta T$  versus the dissipated power P (Eq. 3) in the channel (Fig. 5), where the linear increase of  $\Delta T$  with P can provide the thermal resistance [8] R<sub>th</sub> (Eq.4) by linear regression. Moreover, this allows to extract  $\Delta T$  at the constant P of 1 mW, which is plotted vs temperature in Fig. 6, reporting also the values extracted at constant V<sub>d</sub>. It can be noticed that longer channel present significant difference in  $\Delta T$  according to the employed extraction, while the shorter device seems to display negligible  $\Delta T$  in both cases: the channel of 50 nm is in fact sensibly shorter than the expected mean free path for these devices, which is in the order of 150-200 nm. This means that the short-channel devices are operating in the quasi-ballistic regime, and self-heating occurs mainly at the drain, rather than in the channel. Surprisingly, increased  $R_{\text{th}}$  from phonon radiation at low temperature, which is observed for Si CMOS, is not seen here. Finally, Fig. 7 demonstrates that the HEMTs under study, being bulk-like devices, have a very good heat dissipation (low R<sub>th</sub>), close to state-of-the-art bulk Si CMOS [9] and much better than FDSOI MOSFETs [8].

#### IV. CONCLUSIONS

We have characterized self-heating effects in InGaAs cryogenic HEMTs through gate thermometry and shown that  $R_{th}$  remains fairly constant down to 10 K. The combination of a bulk structure and high mobility enables efficient heat exhaust, resulting in low levels of self-heating. The results build up the understanding of the cryogenic operation of state-of-the-art HEMTs for qubit readout amplification.

#### ACKNOWLEDGMENT

This work was supported by the European Union H2020 program SEQUENCE (Grant – 871764).

$$\begin{aligned} &\text{EQUATIONS} \\ &R_{g} = \Delta V_{g} / \Delta I_{g} \left( 1 \right) \\ \Delta T &= \frac{R_{g,final} - R_{g,initial}}{dR_{g} / dT} \left( 2 \right), \\ &P = I_{d}.V_{d} \left( 3 \right) \\ &R_{th} = \Delta T / P \left( 4 \right) \end{aligned}$$

#### REFERENCES

- [1] Hornibrook et al., Phys. Rev. Appl., vol. 3, no. 2, 2015.

- [2] M. Prathapan et al., WOLTE, 2022, pp. 1-4

- [3] Choi et al., J. Appl. Phys., vol. 130, no. 15, p. 155107, Oct. 2021.

- [4] Ardizzi et al., J. Appl. Phys., vol 132, no. 8, p. 084501 (2022)

- [5] Paliwoda et al., IRPS, 2018, pp. 6E.2-1-6E.2-5

- [6] Su et al., IEEE TED, vol. 41, no. 1, pp. 69-75, Jan. 1994

- [7] Jomaah et al., Solid-State Electron., vol. 38, no. 3, Mar. 1995, pp. 615-618

- [8] Triantopoulos et al., IEEE TED, vol. 66, no. 8, pp. 3498-3505, Aug. 2019,

- [9] Ghibaudo et al., Solid-State Electron., vol. 192, June 2022, 108265

Figure 1. Schematics of the layer-stack of the HEMT devices under study

**Figure 2.** Schematics of the contact pads, with multiple gate-pads dedicated for gate thermometry

Figure 3. Raw measurement of gate resistance thermometry for W = 10  $\mu$ m and Lg = 100 and 200 nm at T = 10 and 300 K

Figure 4. Resistance of the gate metal vs temperature at initial and final stages of measurement for W =  $10\mu m$  and Lg = 200nm

Figure 5. Self Heating for W =  $10\mu m$  and Lg = 200nm versus dissipated power in the channel

Figure 6. Extracted Self Heating for  $W = 10\mu m$  and different channel lengths versus temperature at constant-P (coloured) and constant  $V_d$  (black)

Figure 7. . Thermal resistance versus temperature for different technologies.