## Mapping Hard Real-Time Tasks on Network-on-Chip Manycore Architectures

Chawki Benchehida

#### ▶ To cite this version:

Chawki Benchehida. Mapping Hard Real-Time Tasks on Network-on-Chip Manycore Architectures. Embedded Systems. Université de Lille; Université d'Oran 1, 2021. English. NNT: . tel-03545561v1

### HAL Id: tel-03545561 https://cnrs.hal.science/tel-03545561v1

Submitted on 6 Jan 2022 (v1), last revised 27 Jan 2022 (v3)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# University of Lille University of Oran1

École doctorale des Sciences Pour l'Ingénieur SPI-MADIS

# Mapping Hard Real-Time Tasks on Network-on-Chip Manycore Architectures

#### **Doctoral Thesis**

Computer science

#### Chawki Benchehida

November 09, 2021

| Audrey QUEUDET           | Associate Professor (HDR), University of Nantes, France         | Referee   |

|--------------------------|-----------------------------------------------------------------|-----------|

| Mohamed BENMOHAMMED      | Full Professor, University of Constantine 2, Algeria            | Referee   |

| Sidi Mohammed BENSLIMANE | Full Professor, ESI-SBA, Algeria                                | Examiner  |

| Samia BOUCHERKHA         | Full Professor, University of Constantine 2, Algeria            | Examiner  |

| Houssam Eddine ZAHAF     | Associate Professor, University of Nantes, France               | Examiner  |

| Giuseppe LIPARI          | Full Professor, University of Lille, France                     | Director  |

| Mohammed Kamel BENHAOUA  | Full Professor, University of Mascara, Algeria                  | Director  |

| Abdoulaye GAMATIE        | CNRS Research Director, LIRMM/University of Montpellier, France | President |

|                          |                                                                 |           |

# **Affidavit**

| other than the declared sources/re | is thesis independently, that I have not used sources, and that I have explicitly indicated all either literally or by content from the sources |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                                                                                                                                                 |

| <br>Date                           | <br>Signature                                                                                                                                   |

## **Abstract**

In this dissertation, we tackle the problem of execution complex multi-thread real-time applications on modern Network-on-Chip architectures.

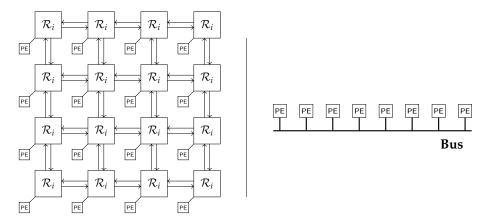

Network-on-Chip (NoC) is a promising technology that fits the increasing performance demands of Cyber-Physical Systems (CPS). The introduction of NoCs is justified by the fact that classical multi-core single-bus architectures fail to address the performance requirements and the predictability needs of modern CPS applications, especially as the number of cores increases. Even if the use of cache memories mitigates the bottleneck effect of single bus architectures, caches introduce unpredictable delays in accessing data, which in turn make it difficult to estimate the execution time of tasks.

Most CPS applications are time-sensitive: tasks are assigned deadlines that must never exceed, otherwise a critical failure may occur. Such systems are denoted by *hard real-time*. Consequently, the communications that occur in the network, denoted by *on-chip communications*, must be predictable and as fast as possible to prevent deadline-missing. Since the task position on the NoC determines its communication cost, the allocation of the application tasks on the chip cores is a crucial problem.

In this thesis, we address specifically the problem of allocating a set of real-time applications, each composed of several parallel tasks, whose structure is described by a Directed Acyclic Graph (DAG), onto a Network-on-Chip processor.

First, we study the problem of bounding the communication cost depending on the different message scheduling policies at the router level. Then we address the problem of task scheduling and of verifying the schedulability of a certain allocation.

Then, we propose an approach to reduce the complexity of the task allocation problem and its analysis cost. Moreover, we propose a task mapping strategy through a meta-heuristic which performs an effective design-space exploration for DAG (Directed Acyclic Graph) tasks. Lastly, in addition to on-chip communications, we studied the mapping problem when the off-chip communications are integrated into the model.

# **Acknowledgments**

I truly believe that the individual success of a person always depends on those behind you. I take this opportunity to thank all those who supported me during my years of thesis. Without them I won't be who I am.

Being part of two teams was an unforgettable experience. First, I would like to thank my first PhD supervisor Prof. Kamel Benhaoua for his guidance, advice, support, trust, and understanding. I also would like to thank my second supervisor Prof. Giuseppe Lipari for his trust, support, advice, and for his great sympathy. Sincerely, I could not have asked for better supervisors than both of you. Furthermore, I want to thank Prof. Mohamed Benmohammed and Dr. Audrey Queudet for their acceptance of being my referees. I would like to thank also my examiners Prof. Sidi Mohammed Benslimane, Prof. Samia Boucherkha, and Prof. Abdoulaye Gamatie for devoting their precious time to review my work. Lastly, I would like to thank Dr. Houssam Eddine Zahaf for being a friend and an exemplary mentor; our scientific discussions were very valuable.

As a PhD student, the teams in which you pertain become the second family. A special thanks go to all my colleague in LAPECI Laboratory for the time spent together and their friendship. Also, I'm blessed to be a member of CRIStAL Laboratory. I would to express my gratitude to Emeraude Team for their kindness and their warm welcome. I won't forget our shared meals and Julien's jokes.

A special thanks to all my friends, so many. Citing you one by one will take the complete acknowledgment section. Thank you to exist.

A special thought to my family, my parents, my sisters Cherifa and Wahiba, all my cousins, my aunts and uncles who have supported me unconditionally.

# **Contents**

| At  | ostrac | t                                           | iii |

|-----|--------|---------------------------------------------|-----|

| Ac  | know   | ledgment                                    | iv  |

| Int | trodu  | ction                                       | 1   |

| ı.  | Ba     | ckground, Context and Related work          | 5   |

| 1.  | Intro  | oduction to Real-Time Systems               | 7   |

|     | 1.1.   | Introduction                                | 8   |

|     | 1.2.   | Task Model                                  | 9   |

|     |        | 1.2.1. Task Dependency                      | 10  |

|     | 1.3.   | Real-time systems scheduling analysis       | 11  |

|     |        | 1.3.1. Scheduling algorithms classification | 11  |

|     |        | 1.3.2. Scheduling characteristics           | 12  |

|     |        | 1.3.3. Scheduling analysis                  | 12  |

|     | 1.4.   | Uniprocessor Scheduling                     | 13  |

|     |        | 1.4.1. Rate Monotonic Scheduling            | 13  |

|     |        | 1.4.2. Deadline Monotonic Scheduling        | 14  |

|     |        | 1.4.3. Earliest Deadline First              | 15  |

|     | 1.5.   | Multiprocessor scheduling                   | 16  |

|     |        | 1.5.1. Partitioned Scheduling               | 17  |

|     |        | 1.5.2. Global Scheduling                    | 18  |

|     |        | 1.5.3. Semi-partitioned Scheduling          | 19  |

|     | 1.6.   | Introduction to parallel programming        | 19  |

|     |        | 1.6.1. Programming real-time systems        | 19  |

|     |        | 1.6.2. POSIX Thread                         | 19  |

|     |        | 1.6.3. Fork-join model                      | 20  |

|     |        | 1.6.4. Message-passing interface            | 20  |

|     | 1.7.   | Conclusion                                  | 21  |

| 2.  | On-    | chip Networks & Manycore architectures      | 23  |

|     | 2.1.   |                                             | 24  |

|     | 2.2.   | Network-on-Chip classes                     | 24  |

|     |        | 2.2.1. Preliminaries                        | 24  |

|     |        | 2.2.2. Circuit-Switched NoCs                | 25  |

|     |        | 2.2.3. Packet-Switching NoCs                | 25  |

|    | 2.3.                                                                               | Network-on-Chip elements                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                      |

|----|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|    |                                                                                    | 2.3.1. Topology                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26                                                                                      |

|    |                                                                                    | 2.3.2. Routing Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                      |

|    |                                                                                    | 2.3.3. Flow Control techniques                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                      |

|    | 2.4.                                                                               | Network-on-Chip routers                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                                      |

|    |                                                                                    | 2.4.1. Virtual Channels                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                                      |

|    |                                                                                    | 2.4.2. Allocators and arbiters                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                      |

|    | 2.5.                                                                               | Industrial Network-on-Chip                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                      |

|    | 2.6.                                                                               | Simulation tools                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34                                                                                      |

|    | 2.7.                                                                               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                                                      |

| 3. | Task                                                                               | « Mapping: Related work                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                      |

|    |                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                      |

|    |                                                                                    | Problem definition                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                                      |

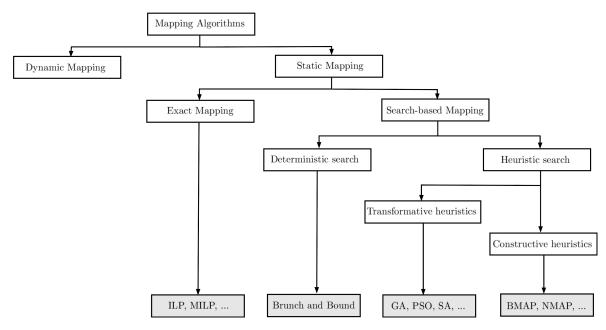

|    | 3.3.                                                                               | N. C.D. 11 ( CD . 1                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                      |

|    |                                                                                    | 3.3.1. Dynamic Mapping                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                      |

|    |                                                                                    | 3.3.2. Static Mapping                                                                                                                                                                                                                                                                                                                                                                                                                              | 38                                                                                      |

|    | 3.4.                                                                               | Safety-critical real-time tasks allocation                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                                      |

|    | 3.5.                                                                               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42                                                                                      |

|    |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| П. | Co                                                                                 | ontributions                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                      |

|    |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

|    |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 4. |                                                                                    | parative study: Priority Preemptive and Round-Robin Arbitration                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                                      |

| 4. | 4.1.                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                                      |

| 4. | 4.1.<br>4.2.                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>48                                                                                |

| 4. | 4.1.                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>48<br>49                                                                          |

| 4. | 4.1.<br>4.2.                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>48<br>49<br>49                                                                    |

| 4. | 4.1.<br>4.2.<br>4.3.                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>48<br>49<br>49<br>51                                                              |

| 4. | 4.1.<br>4.2.                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>48<br>49<br>49<br>51<br>51                                                        |

| 4. | 4.1.<br>4.2.<br>4.3.                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>49<br>49<br>51<br>51<br>52                                                        |

| 4. | 4.1.<br>4.2.<br>4.3.                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>49<br>49<br>51<br>51<br>52<br>53                                                  |

| 4. | 4.1.<br>4.2.<br>4.3.                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54                                            |

| 4. | 4.1.<br>4.2.<br>4.3.                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54                                            |

| 4. | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.                                               | Introduction NoC switching and routing mechanisms System model 4.3.1. Architecture model 4.3.2. Communication model Real-time Communication simulator 4.4.1. Packages 4.4.2. NoC & Simulation Engines Analysis 4.5.1. Fixed priority 4.5.2. Time division multiple access                                                                                                                                                                          | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>54<br>55                                |

| 4. | 4.1.<br>4.2.<br>4.3.                                                               | Introduction NoC switching and routing mechanisms System model 4.3.1. Architecture model 4.3.2. Communication model Real-time Communication simulator 4.4.1. Packages 4.4.2. NoC & Simulation Engines Analysis 4.5.1. Fixed priority 4.5.2. Time division multiple access Experiments                                                                                                                                                              | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>54<br>55<br>55                          |

| 4. | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.                                               | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation                                                                                                     | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>55<br>55<br>56                          |

| 4. | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.                                               | Introduction NoC switching and routing mechanisms System model 4.3.1. Architecture model 4.3.2. Communication model Real-time Communication simulator 4.4.1. Packages 4.4.2. NoC & Simulation Engines Analysis 4.5.1. Fixed priority 4.5.2. Time division multiple access Experiments 4.6.1. Conflicting communications generation 4.6.2. Simulation                                                                                               | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>54<br>55<br>56<br>56                    |

| 4. | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.                                               | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation                                                                                                     | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>55<br>55<br>56                          |

|    | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.                                       | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation  4.6.2. Simulation  Conclusion  Conclusion                                                          | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>54<br>55<br>56<br>56<br>58              |

|    | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.                                       | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation  4.6.2. Simulation  Conclusion  Conclusion  G tasks allocation on NoC  Introduction                 | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>55<br>56<br>56<br>56                    |

|    | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.                                       | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation  4.6.2. Simulation  Conclusion  Conclusion  Related Work                                            | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>55<br>56<br>56<br>58<br><b>61</b><br>62 |

|    | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.<br><b>DAC</b><br>5.1.                 | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation  4.6.2. Simulation  Conclusion  G tasks allocation on NoC  Introduction  Related Work  System Model | 48<br>48<br>49<br>51<br>51<br>52<br>53<br>54<br>55<br>56<br>56<br>58<br><b>61</b><br>62 |

|    | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.<br>4.7.<br><b>DAC</b><br>5.1.<br>5.2. | Introduction  NoC switching and routing mechanisms  System model  4.3.1. Architecture model  4.3.2. Communication model  Real-time Communication simulator  4.4.1. Packages  4.4.2. NoC & Simulation Engines  Analysis  4.5.1. Fixed priority  4.5.2. Time division multiple access  Experiments  4.6.1. Conflicting communications generation  4.6.2. Simulation  Conclusion  Conclusion  Related Work                                            | 48<br>49<br>49<br>51<br>51<br>52<br>53<br>54<br>55<br>56<br>56<br>58<br><b>61</b><br>62 |

|     | 5.4.   | Real-time allocation and schedulability               | 65  |

|-----|--------|-------------------------------------------------------|-----|

|     |        | 5.4.1. Task allocation                                |     |

|     |        | 5.4.2. Communication latency                          | 66  |

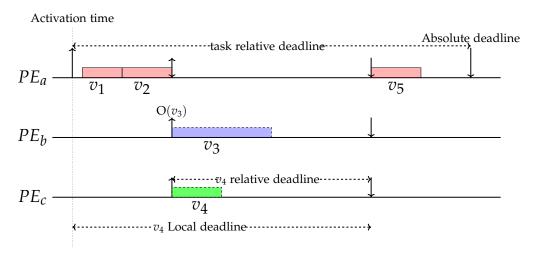

|     |        | 5.4.3. Deadlines and offsets assignment               | 68  |

|     |        | 5.4.4. Single core schedulability analysis            | 70  |

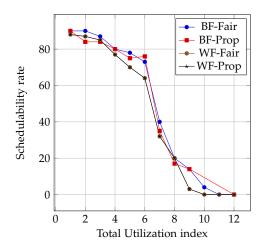

|     | 5.5.   | Results and discussions                               | 71  |

|     | 5.6.   | Conclusion                                            | 71  |

| 6.  | Prod   | cessor-Memory co-scheduling on NoC                    | 73  |

|     | 6.1.   | Introduction                                          | 74  |

|     | 6.2.   | Related work                                          |     |

|     |        | 6.2.1. Real-time tasks allocation                     |     |

|     |        | 6.2.2. Off-chip memory sharing                        |     |

|     | 6.3.   |                                                       |     |

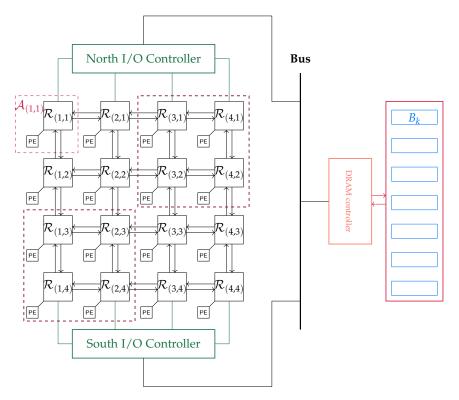

|     |        | 6.3.1. Network-on-Chip design                         |     |

|     |        | 6.3.2. DRAM organization                              | -   |

|     |        | 6.3.3. AER DAG task model                             | 81  |

|     | 6.4.   | MO-SA DAG Task Allocation                             | 83  |

|     |        | 6.4.1. Exploring the neighbor solutions               | 86  |

|     | 6.5.   | AER tasks scheduling analysis and memory latency      | 87  |

|     |        | 6.5.1. Virtual sub-tasks and memory latency cost      | 87  |

|     |        | 6.5.2. On-chip communication latency analysis         |     |

|     |        | 6.5.3. Preemption-cost and AER tasks response time    | 88  |

|     |        | 6.5.4. Offsets and jitters assignment                 | 90  |

|     | 6.6.   | Experimental Results                                  | 91  |

|     |        | 6.6.1. Task set generation                            | 91  |

|     |        | 6.6.2. Bin-packing heuristics                         |     |

|     |        | 6.6.3. Platform specifications & experiments protocol |     |

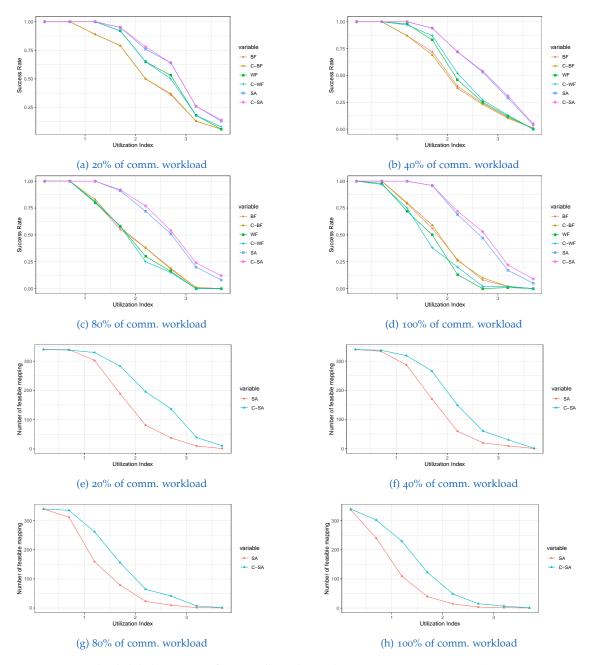

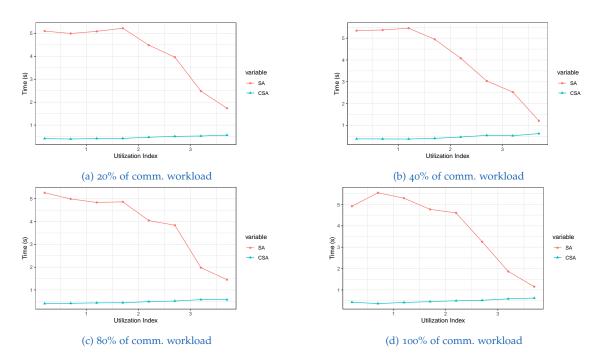

|     |        | 6.6.4. Simulation results and discussions             | 93  |

|     | 6.7.   | Conclusion                                            | 94  |

| Co  | nclus  | sion & Future Works                                   | 99  |

| Pο  | rsons  | al publications                                       | 101 |

|     |        |                                                       |     |

| Bil | bliogr | raphy                                                 | 103 |

# **List of Figures**

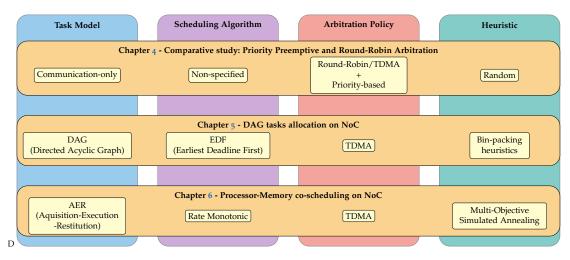

| 0.1.                                                                                           | Contributions schema                                                                                                                                                                                                                                            | 3                                |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| <ol> <li>1.1.</li> <li>1.2.</li> <li>1.3.</li> <li>1.4.</li> <li>1.5.</li> <li>1.6.</li> </ol> | A Cyber-physical System schema                                                                                                                                                                                                                                  | 9<br>10<br>13<br>15              |

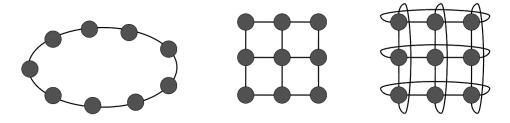

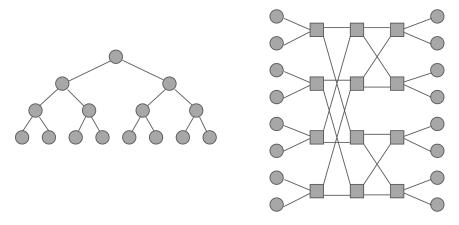

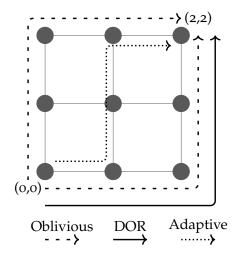

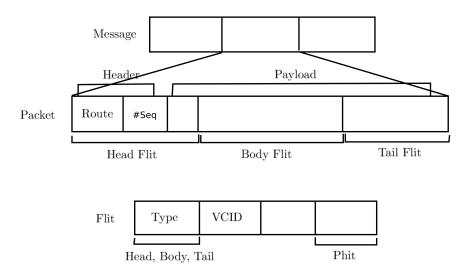

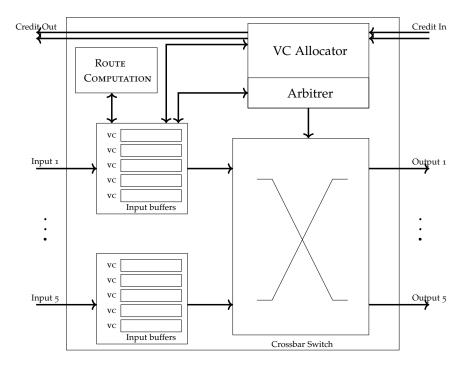

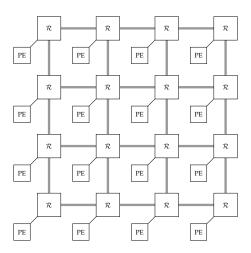

| <ul><li>2.1.</li><li>2.2.</li><li>2.3.</li><li>2.4.</li><li>2.5.</li></ul>                     | 2D-Mesh Network-on-Chip vs. Bus-based Multiprocessor Direct topologies: Ring, 2D-Mesh and torus Indirect topologies: Tree and butterfly Routing algorithms schema Composition of different communication granularity: Message, Packet, Flit Router architecture | 24<br>27<br>28<br>28<br>30<br>31 |

| 3.1.<br>3.2.                                                                                   | Mapping algorithms taxonomy                                                                                                                                                                                                                                     | 37<br>41                         |

| 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.                                                           | 2D-mesh NoC architecture                                                                                                                                                                                                                                        | 50<br>52<br>56<br>57<br>58       |

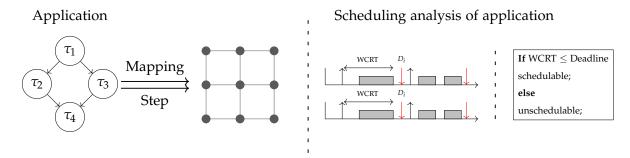

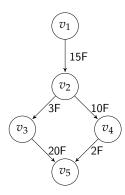

| 5.1.<br>5.2.<br>5·3·                                                                           | An example of a dag task                                                                                                                                                                                                                                        | 65<br>69<br>71                   |

| 6.1.<br>6.2.<br>6.3.<br>6.4.<br>6.5.<br>6.6.                                                   | The execution platform architecture                                                                                                                                                                                                                             | 77<br>80<br>80<br>82<br>83<br>86 |

| 6.8.                                                                                           | $(t_{init} = 1.0, t_{min} = 10^{-3}, t_{\alpha} = 0.90)$                                                                                                                                                                                                        | 95                               |

|                                                                                                | $(t_{init} = 1.0, t_{min} = 10^{-6}, t_{\alpha} = 0.95)$                                                                                                                                                                                                        | 96                               |

6.9. Time related to find the initial solution of both SA and C-SA . . . . 97

# **List of Tables**

|      | A task set with RM priority assignment                                                                                  |    |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 2.1. | Summary of flow control techniques                                                                                      | 30 |

| 3.1. | Summary of the main existing approaches considering real-time applications (ET: Execution Time, EC: Energy Consumption) | 43 |

| 4.1. | NoC configuration and Communication details                                                                             | 57 |

|      | RLDRAM memory access costs                                                                                              | -  |

# **List of Symbols**

```

Task

τ

Γ

Task set

\mathsf{T}_i

Task period

\mathsf{C}_i

Task worst-case execution time (WCET)

D_i

Task deadline

O_i

Task offset

Jitter release

\mathsf{J}_i

\mathcal{J}_i

Job's task

U_i

Utilization rate

Task activation time

a_i

P_i

Task priority

R_i

Task response time

H(\Gamma)

Task set hyperperiod

M

Hardware resource

PΕ

Processing engine

\mathcal{A}

Tile

M

Set of tiles

Set of communications

\mathbb{I}

λ

Unidirectional link

\mathcal{R}

Router

\mathcal{M}

Message

Ρ

Packet

F

FLit

TF(\mathcal{M}_i)

Total number of FLit in a message

\mathcal{V}

Set of vertices

\mathcal{E}

Set of edges

VC

Virtual Channel

Total number of slots by a TDMA cycle

Δ

Path between source and destination sub-tasks

\pi

Task interference

I_i

Sub-task

v_i

\mathcal{C}

Communication between two tasks

lat

Communication latency

e(v_i, v_i)

Edge between two sub-tasks

Sub-task busy period

pred(v_i)

Set of sub-task predecessors

succ(v_i)

Set of sub-task successors

S

Task mapping schema

```

- Front pareto set DRAM Bank Ω

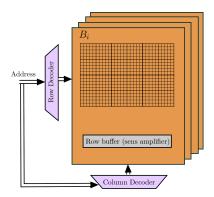

- $B_i$

## Introduction

#### **Objectives & Motivation**

The increasing complexity of modern Cyber-Physical systems (CPS) requires the usage of powerful embedded computing systems to satisfy their timing constraints. Typically, the system monitors a physical environment using sensors, then process and react to the environment state. This sense-compute-react pattern must be completed within a predefined time window imposed by the speed of the environment's evolution. Such constraints are known as real-time constraints. The correctness of the system design relies on its ability to provide guarantees on timing constraints. A violation of a timing constraint might be a serious source of damages.

Classical multi-core platforms design has limited settings in terms of the number of computing resources, which make them inadequate for current and near-future CPS applications. One serious problem of all interconnection architectures based on a single shared bus is that access to memory and devices is exclusive, therefore the bus represents a bottleneck. Even if the use of local cache memories mitigates the performance problems by keeping data on the local cache, it also introduces unpredictable timing to access shared data. This makes it difficult to efficiently bound the execution time of real-time tasks.

**Networks-on-Chip** (also called on-Chip Networks) architectures have been proposed to solve the bus bottleneck problem by providing a more scalable architecture. NoCs can host hundreds of cores on a single chip, connected through a network. Data is moved from one core to another, or to the main memory, by means of network interfaces represented by simple routers. However, these enhanced features increase the complexity, since we have to deal with routing, switching protocols, congestion handling, and classical network problem even when accessing data in the main memory.

Supporting real-time constraints on NoC-based architectures requires particular attention. The system must be predictable, i.e. we must be able to estimate tight and safe bounds for inter-task communications as well as to compute task response time.

The goal of this thesis is to provide support for hard real-time applications on Networks-on-chip. We consider real-time constraints and define NoC parameters and configurations. We propose task and communication mapping such that all deadlines are respected.

In this thesis, we deal with hard-real systems: deadline misses are not tolerable, and the results produced after the deadline are no longer useful. We propose novel techniques and schedulability analyses for a set of real-time tasks modeled by **DAG**s (*Directed Acyclic Graphs*) on NoC resources. Further, we tackle memory-to-chip transfers by extending DAG model to the **AER** (*Acquisition*, *Execute*, *Write-back*) task model.

#### Contribution of this dissertation

**Simulation and analysis of real-time communication** The performance and the real-time behaviour of a Network-on-Chip platform are extremely dependent on the micro-architecture of the routers. In fact, the latter are in charge of regulating the network traffic. Additionally, they also must be designed to deal with real-time constraints: in particular, when multiple incoming flows are directed toward the same output port, the router has to chose which one is sent first by using an arbitration mechanism.

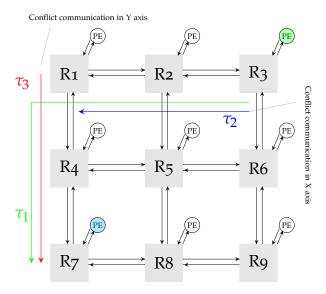

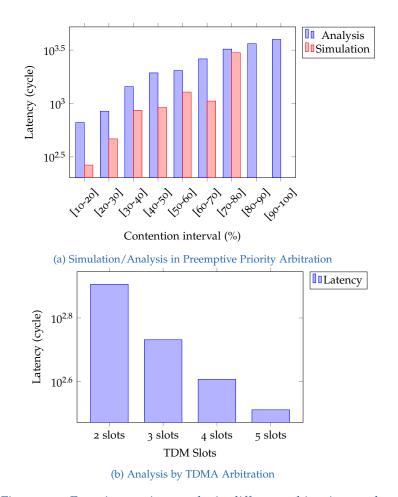

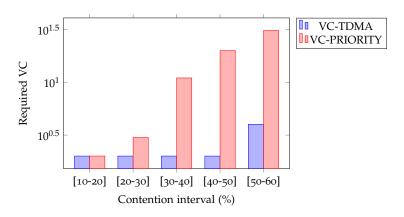

We propose a comparative empirical study on the two main arbitration schemes used in NoC routers, the *priority-preemptive* vs. *round-robin*, onto a mesh-2D network structure. We implemented a simulator that models a wormhole communication mechanism and supports the two policies. Furthermore, we compared analytically the two policies in the worst-case scenario (highest contention rate) by using state-of-the-art formulas.

The goal of this study is to prove that, under *certain assumptions*, the RR protocol can be used as a Guarantee Service (GS) protocol. We compare RR with a priority-preemptive arbitration scheme, and we show that RR can better handle communications in the presence of high workloads and at the same time it is possible to compute an upper bound to the communication delay. We compare the two approaches in order to highlight the gap that separates the two arbitration approaches in the average case. We used both analysis methods and simulations to calculate the task response time in the worst-case and the average case respectively. We conclude that RR can be used in a hard real-time context where deadlinemissing is forbidden.

**Task allocation with earliest deadline scheduling on Network-on-chip** Scheduling real-time tasks on single processor is a research problem that has been widely treated in the literature. However, scheduling real-time tasks on many cores platforms with migration is still an open research problem, and the existing solutions are difficult to deploy on a NoC.

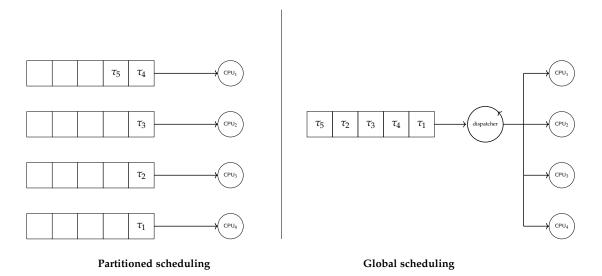

A practical strategy is to transform the many core scheduling problem into a much simpler and well-known problem, the single core scheduling problem. Therefore, in this study, we propose a technique to transform multicores scheduling on several single core scheduling problems by means of partitioned scheduling.

Contrary to global scheduling, partitioned scheduling doesn't allow the task migration.

We used Earliest deadline first (EDF) scheduling policy which is considered as an optimal scheduler on a single core. Therefore, it allows a greater schedulability rate compared to other schedulers. In this study, applications are modelled by a DAG (Directed-Acyclic-Graph) which is an expressive model used to highlight the communications between tasks. The nodes represent the sub-tasks while the edges express the communication between them. We use bin-packing heuristics to prove the efficiency of our contribution.

Memory-aware real-time tasks mapping on Network-on-Chip The problem of mapping a set of independent tasks on a multicore is well-known to be a NP-Hard problem. The complexity increases when considering tasks that communicate and the allocation of tasks' communication. In fact, we distinguish two types of communications: (i) task-to-task communications and (ii) and task-to-main-memory communications (also denoted by off-chip communications). The former regards the communications between sub-tasks whereas the latter concerns the communications between the task and the main-memory (typically, an external DRAM). Thus, finding the optimal system mapping requires sophisticated optimisation techniques. In this work, we propose a task allocation algorithm onto NoC platform based on Simulated Annealing (SA) method.

We choose to use meta-heuristics for their trade-off in providing a reasonable coverage of the design space solution in a reasonable amount of time. To this end, we use an expressive DAG task model that includes the off-chip communications, called **AER** (*Acquisition-Execution-Restitution*) tasks.

#### **Organization**

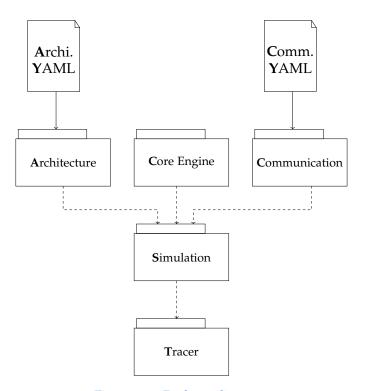

Figure 0.1.: Contributions of this dissertation by elements

In this thesis, we focus on the task mapping problem of hard real-time tasks onto a Network-on-Chip architecture. The problem has been studied in the literature from different points of view, always aiming at providing the best task mapping schema that fits the requirements. Thus, the main contributions of this thesis are:

- Determine the best arbitration mode of Network-on-Chip routers,

- Allocation of DAG tasks onto NoC with earliest deadline scheduling,

- Reducing the worst-case analysis complexity of real-time systems,

- Proposing a predictable Network-on-Chip architecture dealing with off-chip communications,

- Efficient memory-aware task allocation.

Figure 0.1 presents a summary of the thesis contributions by distinguishing the different parts of a study.

This thesis is structured as follows. The first chapter introduces real-time systems and the scheduling theory. The chapter also introduces the schedulability analysis of hard real-time systems in multicores platforms. In chapter two, we give an overview of the Network-on-Chip architecture and its elements. We also present the router's architecture and its features. In chapter three, we introduce the task mapping problem and we present the prior work available in the literature. Chapter four addresses an empirical comparative study between the routers' architectures of the Network-on-Chip. In chapter five, we traits about DAG task mapping technique with partitioned scheduling. We propose a series of transformations to reduce the schedulability analysis complexity. Finally, chapter six addresses the task mapping problem through meta-heuristics onto an execution platform with off-chip memory.

# Part I. Background, Context and Related work

# 1. Introduction to Real-Time Systems

#### **Contents**

| 1.1. | Introd                       | luction                                 |  |  |  |  |  |

|------|------------------------------|-----------------------------------------|--|--|--|--|--|

| 1.2. | Task Model                   |                                         |  |  |  |  |  |

|      | 1.2.1.                       | Task Dependency                         |  |  |  |  |  |

| 1.3. | Real-t                       | ime systems scheduling analysis         |  |  |  |  |  |

|      | 1.3.1.                       | Scheduling algorithms classification 10 |  |  |  |  |  |

|      | 1.3.2.                       | Scheduling characteristics              |  |  |  |  |  |

|      | 1.3.3.                       | Scheduling analysis                     |  |  |  |  |  |

| 1.4. | Unipr                        | ocessor Scheduling                      |  |  |  |  |  |

|      | 1.4.1.                       | Rate Monotonic Scheduling               |  |  |  |  |  |

|      | 1.4.2.                       | Deadline Monotonic Scheduling           |  |  |  |  |  |

|      | 1.4.3.                       | Earliest Deadline First                 |  |  |  |  |  |

| 1.5. | 5. Multiprocessor scheduling |                                         |  |  |  |  |  |

|      | 1.5.1.                       | Partitioned Scheduling                  |  |  |  |  |  |

|      | 1.5.2.                       | Global Scheduling                       |  |  |  |  |  |

|      | 1.5.3.                       | Semi-partitioned Scheduling             |  |  |  |  |  |

| 1.6. | Introd                       | atroduction to parallel programming     |  |  |  |  |  |

|      | 1.6.1.                       | Programming real-time systems           |  |  |  |  |  |

|      | 1.6.2.                       | POSIX Thread                            |  |  |  |  |  |

|      | 1.6.3.                       | Fork-join model                         |  |  |  |  |  |

|      | 1.6.4.                       | Message-passing interface               |  |  |  |  |  |

| 1.7. | Concl                        | usion                                   |  |  |  |  |  |

#### 1.1. Introduction

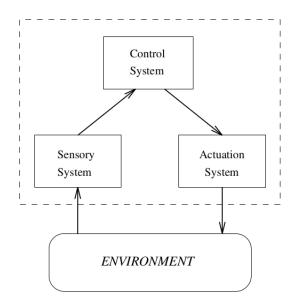

We define a Cyber-physical System (CPS) as a system that interacts with the external environment by means of physical reactions, but not only, as a reaction could be a spoken-order such as a warning or an advice, or simply a meaningful illustration. For instance, the physical reactions are applied by *actuators* and produced after a series of calculations based on a source of data coming from an external acquisition by means of intermediate sensors, cameras, etc. All of flight control systems, automotive applications, and telecommunication systems could be considered in part, or even entirely as CPS. We illustrate in Figure 1.1 a simple CPS schema, where the environment interacts with the system. However, these reactions are sensitive regarding the speed of their executions. In fact, some reactions must be executed before a given time called *deadline*, when exceeding the latter, the result has less importance or any at all. Such systems are denoted as *real-time systems*.

Figure 1.1.: A Cyber-physical System schema

In this section, we introduce real-time systems, a type of time-related systems that are subject to timing constraints. These systems may or may not tolerate deadline-misses depending on their class. We classify real-time systems as follows:

**Hard real-time**: A system is classified as *hard*, if producing the results after the deadline might involve catastrophic scenarios on the system itself.

**Firm real-time**: A system is classified as *firm*, if producing the results after the deadline is useless and doesn't deteriorate the system.

**Soft real-time** : A system is classified as *soft*, if producing the results after the deadline doesn't create consequences, except a performance degradation.

**Definition 1.1.1.** A real-time system is a system which its execution doesn't depends only in the results correctness but also on the time in which the results are produced Stankovic, 1988.

#### 1.2. Task Model

Most real-time systems are modelled as sets of concurrent applications (or *tasks*). In this section we describe the a real-time application as a finite set  $\Gamma$  of *independent* real-time tasks  $\tau$ :  $\Gamma = \{\tau_0, \dots, \tau_n\}$ .

Typically, a independent task can be represented by either the *periodic* task model or the *sporadic* task model. Both models represent an infinite sequence of task instances (refereed by *jobs*). In the periodic task model, the jobs are released strictly periodically, separated by a fixed time value (the period). In the sporadic task model, jobs may arrive at any time, separated by a minimum inter-arrival time.

Each task is characterized by the tuple  $(C_i, D_i, T_i)$  that represents: its worst-case execution time  $C_i$ , its relative deadline  $D_i$ , and its period or minimum inter-arrival time  $T_i$ . The utilization  $U_i$  of a task is calculated by the fraction  $\frac{C_i}{T_i}$ .  $R_i$  denotes the worst-case response time of a task which is the largest interval of time from the release of a job until its completion.

Periodic task set may be classified as *synchronous* if all tasks that compose it are released simultaneously, or *asynchronous* if the tasks are not released at the same time. In the latter case, each task has an offset  $O_i$  that delays its first release.

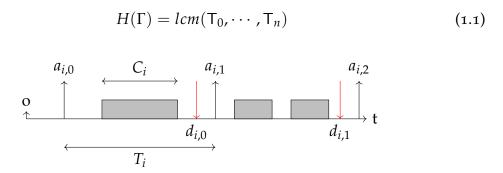

The *hyperperiod*  $H(\Gamma)$  of a task set defines the time at which the complete execution schedule will repeat itself, and it is given by the least common multiple of the task periods (Equation (1.1)).

Figure 1.2.: The sporadic task model

We depict in Figure 1.2 a task model with its characteristics. The literature reports three levels of constraints on task deadline:

- 1. *Implicit deadline*: When the task deadline equals its period  $(D_i = T_i)$ .

- 2. Constrained deadline: When the task deadline is less than or equal its period  $(D_i \leq T_i)$ .

- 3. *Arbitrary deadline*: The task deadline may be less, equal or greater than its period.

Furthermore, a task presents the additional characteristics:

- **Arrival time**  $a_{ij}$ : it is the time at which the j-th job of task  $\tau_i$  is activated and becomes ready for the execution; it is also denoted by the *release time*.

- **Start time**  $s_{ij}$ : it is the time at which the j-th job of task  $\tau_i$  starts its execution.

- **Absolute deadline**  $d_{ij}$ : it is the deadline of the j-th job. The job must execute  $C_i$  units of execution time in interval  $[a_{ij}, d_{ij}]$ .

- **Density**  $\delta_i$ : it's calculated as the ratio  $\delta_i = \frac{C_i}{D_i}$ . Nonetheless, if the deadline is implicit the density equals the task utilization  $U_i$ .

- **Jitter release**  $J_i$ : represent the maximum deviation time that a task can suffer before its start time.

#### 1.2.1. Task Dependency

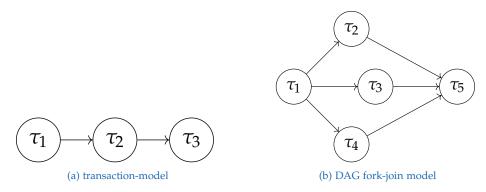

Many real-time systems can be modeled as a set of independent tasks when each of them generates an infinite number of job sequences. However, to meet functional requirements, the system must sometimes be modelled as a set of dependent tasks, which are therefore correlated and must follow an execution order with precedence constraints. Figure 1.3a shows the transaction model, where tasks are to be executed in a pipeline, with each task waiting for the completion of the previous one. Figure 1.3b represents the Directed-Acyclic-Graph (DAG) model which allows more expressive dependencies.

Figure 1.3.: Task dependency levels

A DAG is composed by a set of vertices and edges. The vertices represent computing functions called *sub-tasks* which are typically chunks of the application's code. The edges model communications and precedence constraints between sub-tasks. An edge  $e(v_i, v_j)$  represents a communication between two sub-tasks  $v_i$  and  $v_j$ ; for every  $k \geq 0$ , the k-th instance of subtask  $v_j$  cannot start execution before the k-th instance of subtask  $v_i$  has completed and the corresponding message from  $v_i$  has been received. We call this a *precedence constraint* between  $v_i$  and  $v_j$ .

Consequently, a vertex can be a *source vertex* if it has at least an outgoing edge; and it can be a *destination vertex* is it has one or more incoming edges. A *root vertex* has only outgoing edged and a *sink vertex* has only incoming edges, respectively. Finally, a DAG is *acyclic*: there is no closed cycle in the graph. A DAG is assigned a period  $T_i$  and it can be *periodic* or *sporadic*; it is also characterised by a relative

deadline  $D_i$ , that is the time by which all instances of the subtasks of the DAG must have completed from the corresponding DAG's activation.

#### 1.3. Real-time systems scheduling analysis

Task scheduling defines how the sequence of jobs has to be orchestrated in order to access a resource which could be a calculation unit or a storage medium.

#### 1.3.1. Scheduling algorithms classification

We can classify real-time scheduling algorithms according to the following characteristics:

#### Preemptive vs. Non-Preemptive

- Preemptive algorithms can suspend a running task on a processor, by saving its context, and replace it with another higher priority task.

- In non-preemptive algorithms, once a task has started its execution, it executes until completion with no suspensions, even when higher priority tasks arrive.

#### Static vs. Dynamic

- In static schedulers, all decisions are based on fixed parameters and assigned to tasks before their activation. They are also denoted by *compile-time* scheduling decisions.

- In dynamic schedulers, the decisions are based on dynamic parameters that

may change during the system execution. They are also denoted by run-time

decisions.

#### Off-line vs. Online

- A scheduling algorithm is used off-line if it is executed on the task set before tasks activation. The schedule generated from this operation is stored and later executed by a dispatcher.

- A scheduling algorithm is used on-line if the scheduling decisions are taken at run-time and the schedule may change anytime a new task enters the system.

#### **Optimal vs. Heuristic**

- An algorithm is said to be optimal if it minimizes the cost related to a function defined over the task set.

- An algorithm is said to be heuristic if it is guided by a heuristic function that defines its scheduling decisions.

#### 1.3.2. Scheduling characteristics

A real-time schedule is **correct** if all jobs of all tasks start execution no latter than their arrival time, and complete their execution no earlier than their absolute deadline. A task set that is correctly scheduled by algorithm A is said to be *schedulable* by algorithm A.

Additionally to the scheduling classes, a scheduling algorithm has the following characteristics:

**Optimality**: A scheduler is denoted as optimal with respect to a system and a task model if it can schedule all of the task sets that comply with the task model and are feasible on the system. Davis and Alan Burns, 2011

**Feasibility**: A task set is said to be *feasible* if it exists a scheduling algorithm that generates a correct schedule.

**Predictability**: An algorithm is said to be *predicable* if during the system execution the jobs response time cannot be increased while the task parameters remain constant.

**Comparability**: By comparing two task set by a given scheduling algorithm, there are three possible outcomes

- *Dominance*: Algorithm A is said to *dominate* algorithm B, if all the task sets that are schedulable by B are also schedulable by A and there are task sets schedulable by A, but not according to B.

- *Equivalence*: Algorithm A and B are *equivalent* if all the task set that are schedulable by B are also schedulable by A, and vice-versa.

- *Incomparable*: Algorithm A and B are *incomparable* if there are task sets that are schedulable by B and not by A, and similarly, there are task sets schedulable by A and not by B.

**Sustainability**: An algorithm is said to be *sustainable* associated to a task model, if and only if any task set remains schedulable when: (i) decreasing executions times, (ii) increasing periods or minimum inter-arrival times, and (iii) increasing relative or absolute deadlines.

#### 1.3.3. Scheduling analysis

Assuming a scheduling algorithm and a task set, a *scheduling analysis algorithm* tests the schedulability of the task set with the scheduling algorithm. Typically,

the schedulability test analyses the worst-case scenario of the system. A given schedulability test can be classified as:

**Sufficient test**: A schedulability test is termed sufficient, with respect to a scheduling algorithm and a system if all of the task sets that are deemed schedulable according to the test are in fact schedulable.

**Necessary test** Conversely, a schedulability test is termed necessary if all of the task sets that are deemed unschedulable according to the test are in fact unschedulable.

**Exact test** If the schedulability test is both sufficient and necessary.

#### 1.4. Uniprocessor Scheduling

In this section, we introduce uniprocessor scheduling and the different scheduling algorithms associated to it. We will facilitate the functioning of the algorithms by bringing some simple examples.

#### 1.4.1. Rate Monotonic Scheduling

The rate monotonic scheduling belongs to the *fixed-priority scheduling class* of algorithms. It simply assigns priorities to tasks according to their rates (inverse of the periods). Specifically, tasks with shorter periods will have higher priorities. We denote the task priority by  $P_i$ .

| Γ       | $C_i$ | $T_i$ | $P_i$ |

|---------|-------|-------|-------|

| $	au_1$ | 2     | 6     | 1     |

| $	au_2$ | 3     | 8     | 2     |

Table 1.1.: A task set with RM priority assignment

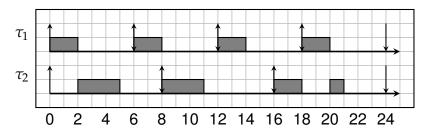

Figure 1.4.: The RM tasks scheduling

**Example 1.4.1.** Let define  $\Gamma$  a task set with two periodic tasks with implicit deadline (task characteristics are in Table 1.2)

$$U = \sum_{i=1}^{n} \frac{\mathsf{C}_i}{\mathsf{T}_i} = \frac{2}{6} + \frac{3}{8} \approx 0.70 \tag{1.2}$$

When task set utilization  $U_i$  remains under  $n(2^{1/n} - 1)$  (n represents the task set cardinality) Liu and Layland, 1973 all the task are schedulable. Thus, the latter value constitutes the feasibility upper bound of RM.

#### 1.4.2. Deadline Monotonic Scheduling

The DM scheduling algorithm is similar to RM since they pertain to the same class of fixed-priority schedulers. RM assigns the priority according to the relative deadline: tasks with shorter deadlines have higher priorities. The algorithm has been proposed by Leung and Whitehead J. Y.-T. Leung and Whitehead, 1982 to tasks with *constrained deadline*.

The feasibility of a task set with constrained deadline can be guaranteed using the utilization based sufficient scheduling test:

$$\sum_{i=1}^{n} \frac{\mathsf{C}_{i}}{\mathsf{D}_{i}} \le n(2^{1/n} - 1) \tag{1.3}$$

To find a necessary and sufficient schedulability test for DM, N. Audsley et al., 1993 proposed an efficient test for periodic tasks, called *response time analysis*. The proposed method computes the longest response time  $R_i$  of a periodic task  $\tau_i$  at the critical instant which is the sum of its computation time and the interference  $I_i$  of higher priority tasks:

$$R_i = C_i + I_i$$

where

$$I_i = \sum_{j \in hp(i)} \left\lceil \frac{R_i}{\mathsf{T}_j} \right\rceil \cdot \mathsf{C}_j$$

Hence,

$$R_i^{(n+1)} = \mathsf{C}_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i^{(n)}}{\mathsf{T}_j} \right\rceil \cdot \mathsf{C}_j \tag{1.4}$$

The calculation of  $R_i$  in Equation 1.4 is performed iteratively by defining:  $R_i^{(0)} = C_i$ . The stop condition of the iteration is either when:  $R_i^{n+1} = R_i^n$  or  $R_i > D_i$ . The system is declared as not schedulable when the latter condition occurs.

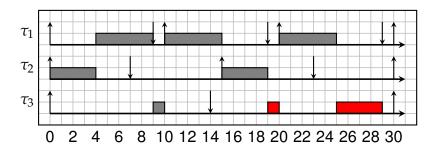

| Γ       | $C_i$ | $T_i$ | $D_i$ | $P_i$ | $R_i$ |

|---------|-------|-------|-------|-------|-------|

| $	au_1$ | 5     | 10    | 9     | 2     | 9     |

| $	au_2$ | 4     | 15    | 7     | 1     | 4     |

| $	au_3$ | 6     | 30    | 14    | 3     | 15    |

Table 1.2.: A task set with DM priority assignment

Figure 1.5.: The DM task scheduling (unschedulable case)

#### 1.4.3. Earliest Deadline First

Earliest Deadline First (EDF) is an algorithm that selects jobs according to their absolute deadline. Specifically, jobs with earlier deadlines have a higher priority. Thus, the more a task execution is close to its deadline, the higher is its priority. The absolute deadline of a periodic task is calculated as following:

$$d_{i,j} = O_i + (j-1)T_i + D_i$$

(1.5)

EDF is a dynamic priority assignment. Typically, tasks are executed in preemptive mode since the current active task can be replaced by a task with an earlier deadline.

Concerning the implicit deadline task sets ( $T_i = D_i$ ), the schedulability analysis under EDF can be verified through the processor utilization factor. Thus, EDF is known to be optimal since the tasks remain schedulable when the processor utilization up to 100%, by the following sufficient condition:

$$\sum_{i=1}^{n} \frac{\mathsf{C}_i}{\mathsf{T}_i} \le 1 \tag{1.6}$$

#### **Demand Bound Function**

Under EDF, the analysis of periodic tasks with *constrained deadline* ( $D_i < T_i$ ) can be performed using the *processor demand* metric. We refer this method to the work of Sanjoy K Baruah, Louis E Rosier, and Rodney R Howell, 1990a.

The processor demand of a task  $\tau_i$  in an interval  $[t_1, t_2]$  is expressed by the amount of processing time  $g_i(t_1, t_2)$  requested by the sequence of jobs activated in  $[t_1, t_2]$  and must be completed in the same interval, such that:

$$g_i(t_1, t_2) = \sum_{r_{i,k} \ge t_1, d_{i,k} \le t_2} C_i$$

(1.7)

However, when the task set is synchronous, which means all tasks are released simultaneously and activated at t = 0 (i.e.  $\Phi_i = 0$  for all the tasks), we must verify the demand of all jobs in [0,t]. Consequently, we use the *Demand Bound Function* Sanjoy K Baruah, Louis E Rosier, and Rodney R Howell, 1990a:

$$dbf(t) = \sum_{i=1}^{n} \left\lfloor \frac{t + T_i - D_i}{T_i} \right\rfloor \cdot C_i$$

(1.8)

Thus, a synchronous set of periodic tasks with constrained deadline is schedulable by EDF if and only if Equation (1.9) is verified.

$$\forall t > 0 \quad \mathsf{dbf}(t) \le t \tag{1.9}$$

#### 1.5. Multiprocessor scheduling

This section introduces the multiprocessors systems and some terminology and notation used in multiprocessors scheduling research. Moreover, we related a taxonomy of multiprocessors scheduling and develop each part in a dedicated section. Unlike the uniprocessor scheduling, the multiprocessor scheduling must face the two following problem:

- *The allocation problem*: on which processor a task should execute.

- *The priority problem*: when, and in what order should a job execute regarding the sequence of jobs of other tasks.

We can distinguish through Figure 1.6 the difference between the partitioned and the global scheduling when the former has a queue for each processor, whereas the latter gathers all the tasks into one queue and dispatches the tasks to processors.

On the other hand scheduling algorithms can be classified according to the task migration tolerance and priority changing in run-time (See Carpenter et al., n.d. for more details) as follows:

Figure 1.6.: Partitioned vs. global scheduling

#### **Allocation-based classification**

- *No migration*: Each task is definitively allocated to a processor and no migration is permitted.

- *Task-level migration*: The jobs that pertain to a task may execute on different processors. However, each job can only execute on a single processor.

- *Job-level migration*: It's permitted to a job to migrate to a different processor during its execution.

#### **Priority-based classification**

- *Fixed task priority*: Each task receives a fixed priority that will be applied to all of its jobs.

- *Fixed job priority*: The jobs of the same tasks may have different priorities, but each job has a signle static priority. EDF is considered from this class.

- *dynamic priority*: A single job may have different priorities during its execution, as Least Laxity First (LLF) scheduling.

#### 1.5.1. Partitioned Scheduling

The partitioned scheduling doesn't allow task migration. At this fact, it has the advantages of:

- There is no migration cost to consider or any interference related to the migration process, which renders the schedulability analysis easy.

- If a task exceeds its worst-case execution time budget, it impacts only the tasks on the same processor.

• The partitioned approaches use a separate run-queue per processor, rather than a single global queue. Therefore, the overheads of queue manipulating is less important onto large systems.

#### Task partitioning strategies

Determining an optimal task partitioning is known to be an NP-Complete problem in the strong sense, where is usually described as a bin-packing problem. Since each partitioning heuristic has its own strategy, several of them consist of two phases according to S. Baruah and Fisher, 2005:

- The pre-processing phase where the tasks are pre-sorted according to a task parameter, e.g., according to the shortest deadline in DM or the task utilization.

- The assignment phase which consists of placing tasks into processors.

There are usual assignment strategies commonly used for task partitioning:

- First-Fit (FF): The task is always allocated to the first processor that fits its demand while processors are increasingly sorted based on their ID.

- Best-Fit (BF): The task is allocated to the first processor while the set of processors is sorted in decreasing order with respect to their utilization.

- Worst-Fit (WF): Similar to BF, but the processors are sorted in increasing order with respect to their utilization.

- Arbitrary-Fit (AF): Each task is assigned to a processor in random order.

#### 1.5.2. Global Scheduling

Unlike the partitioned scheduling, this class of algorithms allows the task migration from one processor to another. Global scheduling presents the following advantages compared to partitioned scheduling:

- It experiences only fewer context switches/preemptions when it is deployed, as the scheduler preempts tasks when there are no idle processors Andersson and Jonsson, 2000.

- The processor availability (space capacity) when a task executes less than its worst-case execution time which can be used by all other tasks, not just those on the same processor.

- It is typically more appropriate to open systems, as there is no need to run load balancing or task re-scheduling when the set of tasks changes.

Global-EDF and Global-DM are examples of the adaptation of uniprocessor schedulers to global scheduling. The priority assignment logic doesn't change but it allows the *m* highest tasks/jobs to run in parallel and at the same time. Usually, when a task arrives and there is no idle processor, it preempts a lower priority task and executes on the freed processor.

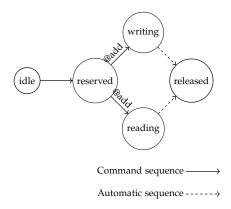

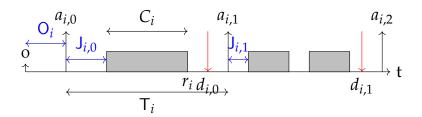

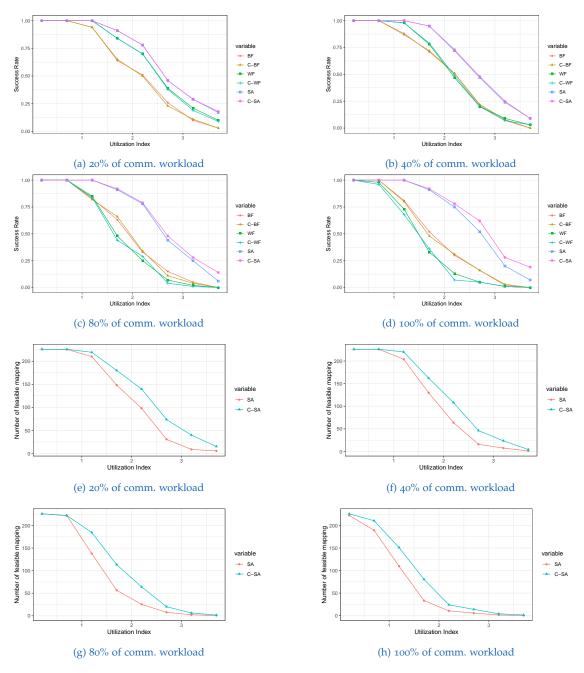

#### 1.5.3. Semi-partitioned Scheduling