# A Lightweight Host-based Intrusion Detection System using a Hardware-Assisted Monitor to detect Wireless Attacks Targeting Constrained IoT Devices

Mohamed El-Bouazzati

#### ▶ To cite this version:

Mohamed El-Bouazzati. A Lightweight Host-based Intrusion Detection System using a Hardware-Assisted Monitor to detect Wireless Attacks Targeting Constrained IoT Devices. Embedded Systems. Université de Bretagne Sud, 2023. English. NNT: . tel-04612764

# HAL Id: tel-04612764 https://cnrs.hal.science/tel-04612764

Submitted on 14 Jun 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

L'Université Bretagne Sud

ÉCOLE DOCTORALE Nº 644

Mathématiques et Sciences et Technologies

de l'Information et de la Communication en Bretagne Océane

Spécialité: Informatique et Architectures Numériques

Par

# **Mohamed EL BOUAZZATI**

A Lightweight Host-based Intrusion Detection System using a Hardware-Assisted Monitor to detect Wireless Attacks Targeting Constrained IoT Devices

Thèse présentée et soutenue à Lorient, le 05 Decembre 2023

Unité de recherche : Lab-STICC UMR 6285

Thèse Nº: 685

#### Rapporteurs avant soutenance:

Aurélien FRANCILLON Professeur des Universités - EURECOM, Biot, FR

Vincent NICOMETTE Professeur des Universités - LASS-CNRS, INSA, Toulouse, FR

**Composition du Jury:**

Président : Daniela DRAGOMIRESCU Professeur des Universités - LAAS-CNRS, INSA, Toulouse, FR

Examinateurs: Aurélien FRANCILLON Professeur des Universités - EURECOM, Biot, FR

Pierre-François GIMENEZ Maître de Conférences - IRISA, CentraleSupélec, Rennes, FR Vincent NICOMETTE Professeur des Universités - LAAS-CNRS, INSA, Toulouse, FR

Russell TESSIER Professeur des Universités - University of Massachusetts, Amherst, USA

Dir. de thèse : Guy GOGNIAT Professeur des Universités - Lab-STICC, Université Bretagne Sud, Lorient, FR Co-dir. de thèse : Philippe TANGUY Maître de Conférences - Lab-STICC, Université Bretagne Sud, Lorient, FR

# **ACKNOWLEDGEMENT**

Throughout my academic journey, I have been grateful for the support of a vast network of people whose advice and guidance were key in helping me to achieve my PhD.

I would like to express my deep gratitude for the continuing support of my thesis supervisors, Professor Guy Gogniat and Associate Professor Philippe Tanguy. Their advice and confidence in my abilities have been the keystone of my academic achievements.

Throughout my PhD, I also had the privilege of collaborating with an international laboratory and being hosted as a visiting researcher at the University of Massachusetts. I am very grateful to Professor Russell Tessier for his invaluable advice and support during and after this period. His mentorship has been crucial to the success of my research.

I extend my gratitude to the respected jury members: Daniela Dragomirescu of INSA Toulouse, France; Vincent Nicomette of INSA Toulouse, France; Russell Tessier of the University of Massachusetts, Amherst, MA, USA; Aurélien Francillon of EURECOM, Biot, France; and Pierre-François Gimenez of CentraleSupélec, Rennes, France. I sincerely appreciate the time they dedicated to reviewing this manuscript and the constructive remarks they provided. I would also like to thank Pascal Benoit and Bertrand Legal for having participated in my CSI (Comité de Suivi Individuel). Their scientific discussions and insightful advice played a crucial role in shaping my thesis.

My heartfelt thanks go to my friends and colleagues at Lab-STICC and other laboratories who have made a significant contribution to the productivity of my working environment. I am particularly grateful to Béatrice Guern, Virginie Guillet, Florence Palin and Noluenn Chauvin for their immeasurable help in various administrative aspects. Their support was crucial and I am grateful for their dedicated efforts.

My warmest thanks go to my whole family: my parents, my brothers, my sister and my wife for their unconditional love and support.

# **ACRONYMS**

**ASIC** Application Specific Integrated Circuit.  $\mathbf{B}$ **BLE** Bluetooth Low Energy.  $\mathbf{C}$ CPU Central Processing Unit. CPUs Central Processing Units. CRC Cyclic Redundancy Check. CSR Control Status Register. D **DDoS** Distributed Denial of Service. **DoS** Denial of Service.  $\mathbf{E}$ EWMA Exponentially Weighted Moving Average.  $\mathbf{F}$ **FPGA** Field Programmable Gate Array. **FSM** Finite State Machine.  $\mathbf{H}$ **HIDS** Host-Based Intrusion Detection System. **HPC** Hardware Performance Counter.  $\mathbf{HPM}$  Hardware Performance Monitoring. **HPMtracer** Hardware Performance Monitoring Tracer.

$\mathbf{A}$

Ι

**IDS** Intrusion Detection System.

**IoT** Internet of Things.

**ISA** Instruction Set Architecture.

$\mathbf{L}$

LCL Lower Control Limit.

$\mathbf{M}$

MAC Media Access Control.

MCU Microcontroller Unit.

MITM Man in the Midlle.

$\mathbf{N}$

**NIDS** Network-Based Intrusion Detection System.

**NwHPC** Network Hardware Performance Counter.

O

**OTA** Over the Air.

P

PHY Physical.

PLR Packet Loss Rate.

$\mathbf{R}$

**RCE** Remote Code Execution.

**RF** Radio Frequency.

**RSSI** Received Signal Strength Indicator.

$\mathbf{S}$

SDR Software Defined Radio.

**SF** Spreading Factor.

**SIMD** Single Instruction Multiple Data.

${f SNR}$  Signal Noise Ratio.

${\bf SoC}\,$  System on Chip.

SoCs Systems on Chip.

$\mathbf{U}$

${\bf UCL} \ \ {\bf Upper} \ {\bf Control} \ {\bf Limit}.$

# **LIST OF FIGURES**

| 1.1  | Internet of Things (IoT) Environment Architecture                                   | 14 |

|------|-------------------------------------------------------------------------------------|----|

| 2.1  | Block Diagram of System on Chip (SoC) for IoT end-devices                           | 20 |

| 2.2  | IoT Stack Layers                                                                    | 24 |

| 2.3  | Wireless Connectivity SoC Technologies                                              | 26 |

| 2.4  | IoT SoC Attacks Entry Points                                                        | 29 |

| 2.5  | IDS Taxonomy for IoT Environment                                                    | 37 |

| 3.1  | IoT Wireless Connectivity with considered Threat Model                              | 46 |

| 3.2  | Diwall Approach                                                                     | 49 |

| 3.3  | Example : Diwall Chronogram with IoT Stack                                          | 49 |

| 3.4  | Block Diagram of CV32E40P 32 bits RISC-V Software Core $\ \ldots \ \ldots \ \ldots$ | 50 |

| 3.5  | SoC of Wireless Connectivity and Network Processor Testbed for Training             | 54 |

| 3.6  | SoC of Wireless Connectivity and Network Processor Testbed for Diwall               |    |

|      | Test and Validation                                                                 | 56 |

| 3.7  | Frequency Histogram of Microarchitectural Metrics monitored with Hard-              |    |

|      | ware Performance Monitoring Tracer (HPMtracer)                                      | 58 |

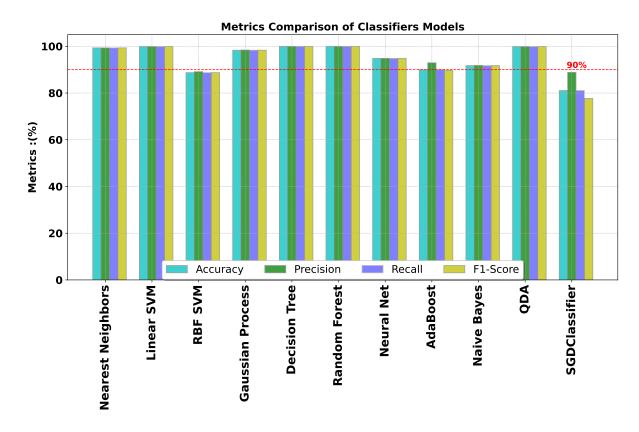

| 3.8  | Machine Learning Classifiers Comparison Accuracy                                    | 61 |

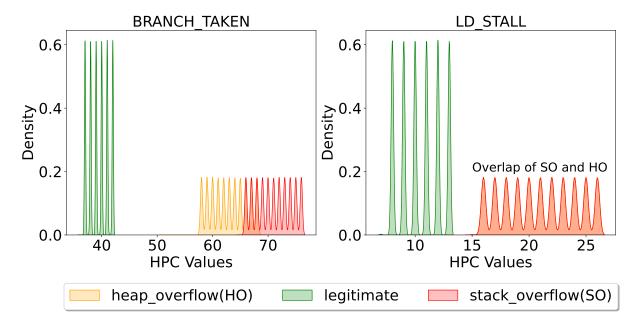

| 3.9  | Selected Microarchitectural Metrics by Decision Tree Model                          | 63 |

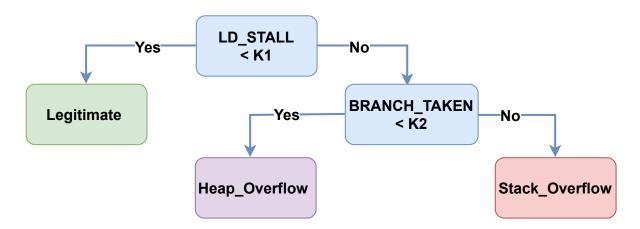

| 3.10 | Generated Decision Tree Classifier Model                                            | 64 |

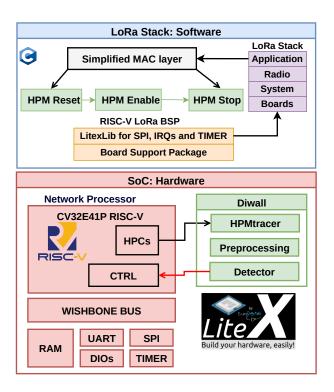

| 3.11 | SoC Architecture with LoRaMACnode stack                                             | 66 |

| 3.12 | Trigger and Continuous Jamming Categories                                           | 67 |

| 3.13 | LoRa Testbed with Diwall implemented on Field Programmable Gate Ar-                 |    |

|      | ray (FPGA) Arty A7 100T Board                                                       | 68 |

| 3.14 | Received Signal Strength Indicator (RSSI) and Signal Noise Ratio (SNR)              |    |

|      | Metrics during Legitimate Traffic and Jamming                                       | 69 |

| 3.15 | RSSI and Hardware based Exponentially Weighted Moving Average (EWMA) $$             |    |

|      | during Legitimate Traffic and Jamming Attacks                                       | 71 |

| 4.1  | CV32E40P Architecture Integrating Diwall                                            | 77 |

#### LIST OF FIGURES

| 4.2 | Block diagram illustrating the architecture of Diwall incorporating ${\rm CV32E40P}$ |    |  |  |  |

|-----|--------------------------------------------------------------------------------------|----|--|--|--|

|     | Processor                                                                            | 78 |  |  |  |

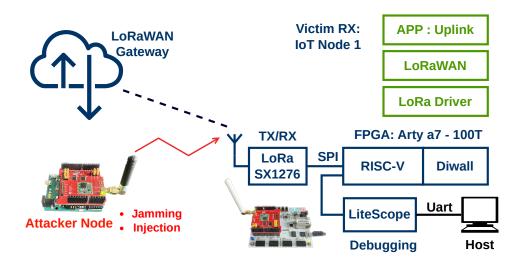

| 4.3 | Evaluation of Diwall on FPGA Arty A7 100T Board within LoRa Testbed                  | 84 |  |  |  |

| 4.4 | LoRaMac-node Stack and LoRa Driver with RISC-V BSP                                   | 90 |  |  |  |

| 4.5 | Testbed Evaluation of Detection Rates for Diwall in LoRaWAN Networks .               | 93 |  |  |  |

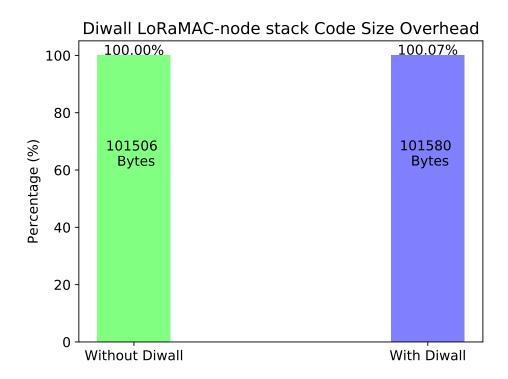

| 4.6 | Code Size Percentage Comparison with and without Diwall Integration                  |    |  |  |  |

|     | Overhead                                                                             | 94 |  |  |  |

# LIST OF TABLES

| 2.1 | Industrial IoT SoCs Features Comparison                                             | 22 |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of Research SoCs Features                                                | 23 |

| 2.3 | Comparison of Network Processor Architectures in Research                           | 28 |

| 2.4 | Security State-of-the-Art IoT Low Data-Rate Protocols (LoRaWAN, Zig-                |    |

|     | Bee, Bluetooth Low Energy (BLE))                                                    | 32 |

| 2.5 | Industrial IoT SoCs Security Features Comparison                                    | 35 |

| 2.6 | Network-based Intrusion Detection System (IDS) for IoT $\ \ldots \ \ldots \ \ldots$ | 38 |

| 2.7 | Diwall and Related Works for Host-Based Intrusion Detection System (HIDS)           |    |

|     | in IoT                                                                              | 41 |

| 3.1 | List of Hardware Microarchitectural Events Monitored by the CV32E40P                |    |

|     | Hardware Performance Counter (HPC)s                                                 | 52 |

| 3.2 | Attacks Scenarios: The buffer size is 10 or 23 bytes. Larger Packets result         |    |

|     | in a Buffer Overflow                                                                | 57 |

| 4.1 | Resource Utilization and Maximum Frequency of Implementation for 5                  |    |

|     | Versions of the Network Processor with and without Diwall                           | 83 |

| 4.2 | Evaluation of Diwall Detection Rates for Packet Injection Attacks                   | 87 |

| 4.3 | Evaluation of Diwall Detection Rates for Jamming Attacks                            | 87 |

| 4.4 | Diwall Detection Rates in LoRaWAN Network                                           | 93 |

# **TABLE OF CONTENTS**

| A        | crony | ms     |                                            | 4  |

|----------|-------|--------|--------------------------------------------|----|

| Li       | st of | Figur  | es                                         | 8  |

| Li       | st of | Table  | S                                          | 9  |

| 1        | Intr  | oducti | ion                                        | 13 |

|          | 1.1   | Conte  | ${f xt}$                                   | 13 |

|          | 1.2   | Motiv  | ation                                      | 15 |

|          | 1.3   | Contr  | ibutions and Organization of Manuscript    | 16 |

|          |       | 1.3.1  | Contributions                              | 16 |

|          |       | 1.3.2  | Organization                               | 17 |

| <b>2</b> | Syst  | tem-or | n-Chip for IoT and Wireless Security       | 19 |

|          | 2.1   | SoC fo | or Low-Power and Low-Data-Rate End-Devices | 19 |

|          |       | 2.1.1  | SoC Overview                               | 19 |

|          |       | 2.1.2  | SoC in Industry                            | 20 |

|          |       | 2.1.3  | SoC in Research                            | 21 |

|          | 2.2   | SoC V  | Vireless Connectivity                      | 23 |

|          |       | 2.2.1  | IoT Protocol Stack                         | 23 |

|          |       | 2.2.2  | Considered Waveforms                       | 24 |

|          |       | 2.2.3  | Network Processor Architectures            | 25 |

|          | 2.3   | Securi | ty of SoC Wireless Connectivity            | 28 |

|          |       | 2.3.1  | Attack Entry Points                        | 28 |

|          |       | 2.3.2  | Vulnerabilities                            | 29 |

|          |       | 2.3.3  | Attacks                                    | 31 |

|          |       | 2.3.4  | Security Mechanisms                        | 34 |

|          | 2.4   | Intrus | ion Detection System - IDS                 | 36 |

|          |       | 2.4.1  | IDS Overview and Taxonomy                  | 36 |

|          |       | 2 4 2  | Network-Based IDS                          | 37 |

|   |     | 2.4.3   | Host-Based IDS                                  | 39         |

|---|-----|---------|-------------------------------------------------|------------|

|   |     | 2.4.4   | Identified Challenges                           | 41         |

|   | 2.5 | Summ    | ary                                             | 43         |

| 3 | Diw | all: H  | ost-based Intrusion Detection System            | 45         |

|   | 3.1 | Threat  | t Model                                         | 45         |

|   | 3.2 | Propos  | sed HIDS: Diwall                                | 47         |

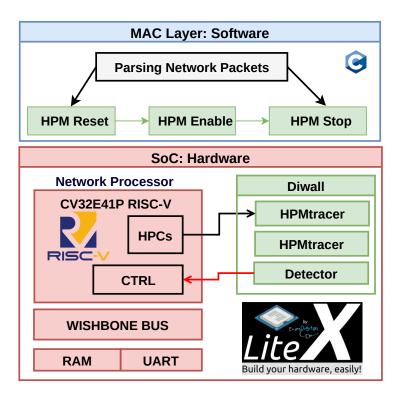

|   |     | 3.2.1   | Key Features                                    | 47         |

|   |     | 3.2.2   | Overview                                        | 47         |

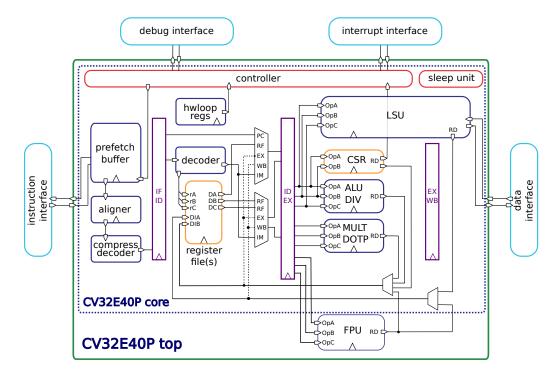

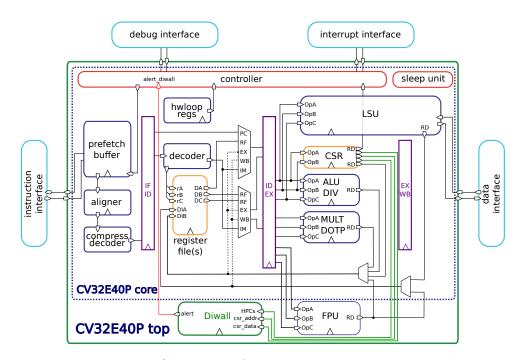

|   |     | 3.2.3   | Target CPU                                      | 50         |

|   |     | 3.2.4   | Metrics                                         | 51         |

|   | 3.3 | Study   | of Packet Injection Attacks                     | 53         |

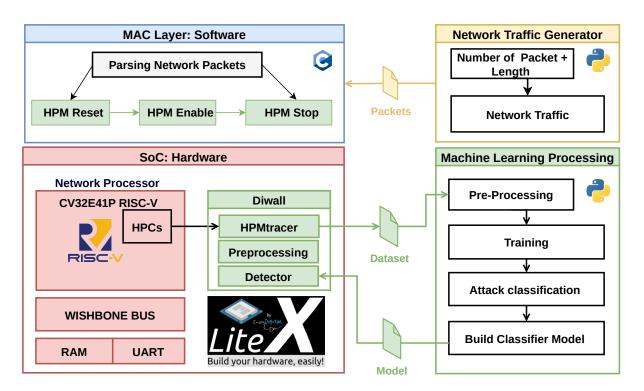

|   |     | 3.3.1   | Simulation Experimental Setup                   | 53         |

|   |     | 3.3.2   | Packet Injection Reproduction Attacks           | 55         |

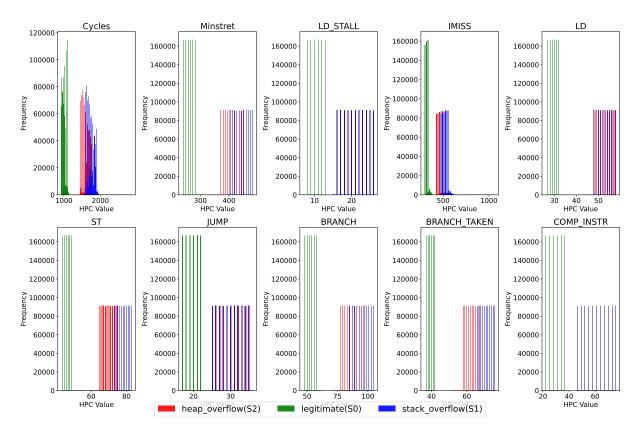

|   |     | 3.3.3   | Dataset Generation                              | 57         |

|   |     | 3.3.4   | Machine Learning Classification                 | 59         |

|   |     | 3.3.5   | Decision Tree Classifier Model                  | 62         |

|   |     | 3.3.6   | Conclusion                                      | 64         |

|   | 3.4 | Study   | of Jamming Attacks                              | 65         |

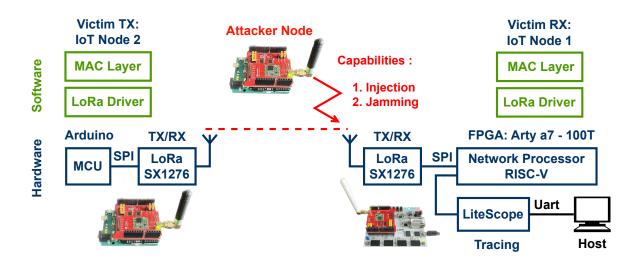

|   |     | 3.4.1   | FPGA Experimental Testbed                       | 65         |

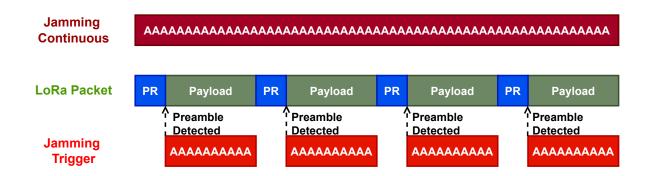

|   |     | 3.4.2   | Jamming Reproduction Attacks                    | 66         |

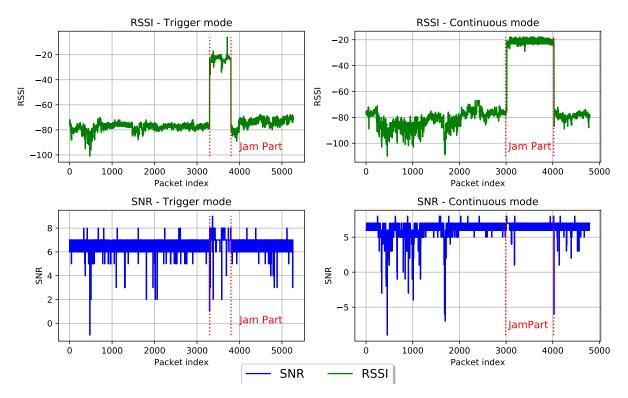

|   |     | 3.4.3   | Dataset Generation                              | 67         |

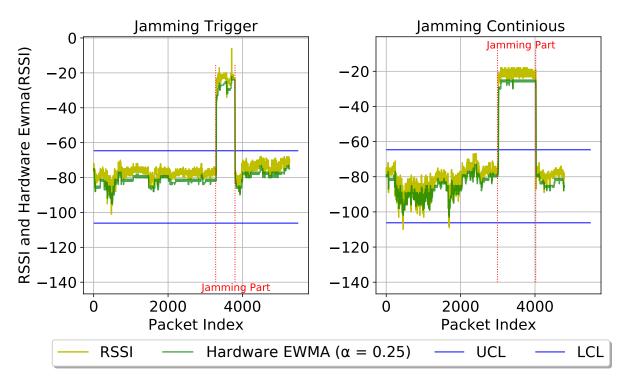

|   |     | 3.4.4   | Jamming Detection Methodology                   | 69         |

|   |     | 3.4.5   | Conclusion                                      | 72         |

|   | 3.5 | Summ    | ary                                             | 73         |

| 4 | Diw | all: In | aplementation and Experimental Evaluation       | <b>7</b> 6 |

|   | 4.1 | Diwall  | FPGA Implementation                             | 76         |

|   |     | 4.1.1   | Diwall Architecture Implementation              | 76         |

|   |     | 4.1.2   | HPMtracer: Hardware Tracer                      | 78         |

|   |     | 4.1.3   | Preprocessing                                   | 79         |

|   |     | 4.1.4   | Detector: Decision Tree and EWMA Control Limits | 79         |

|   |     | 4.1.5   | Diwall Configuration                            | 80         |

|   |     | 4.1.6   | FPGA Resource and Performance Overhead          | 82         |

|   | 4.2 |         | imental Evaluation Framework                    | 83         |

#### TABLE OF CONTENTS

|         | 4.2.1    | LoRa and Simplified MAC Layer        | . 84  |

|---------|----------|--------------------------------------|-------|

|         | 4.2.2    | Results                              | . 86  |

|         | 4.2.3    | Discussion                           | . 88  |

| 4.3     | Use Ca   | ase: LoRaWAN with <i>Diwall</i>      | . 89  |

|         | 4.3.1    | LoRaWAN Testbed                      | . 89  |

|         | 4.3.2    | Results                              | . 93  |

|         | 4.3.3    | Discussion                           | . 95  |

| 4.4     | Conclu   | sion                                 | . 96  |

| Conclu  | sion &   | Future Perspectives                  | 99    |

| Conc    | clusion. |                                      | . 99  |

| Futu    | re Worl  | k & Perspectives                     | . 101 |

|         | 4.4.1    | Improvements to Requirements Covered | . 102 |

|         | 4.4.2    | Flexibility and Security of Diwall   | . 103 |

| Publica | ations a | and Presentations                    | 105   |

| Bibliog | raphy    |                                      | 107   |

# INTRODUCTION

#### 1.1 Context

The Internet of Things (IoT) domain has experienced exceptional growth in recent decades and has become an integral part of the world. This has brought significant transformations to various aspects of our lives, enabling continuous data monitoring and real-time remote system control. IoT applications span across sectors, such as healthcare, smart homes, smart cities, agriculture, and industrial automation. Consumer IoT products are being increasingly integrated into daily routines. The spread of IoT devices has been remarkable, with billions now in use globally. For instance, in 2020, the European commission reported in [1] that 51% of individuals in Europe are using IoT devices such as smart TVs, game consoles, home audio systems, and smart speakers. The global IoT market reached 16.7 billion devices and is projected to grow to 29.7 billion by 2027 [2]. The economic impact of IoT is substantial, with worldwide consumer IoT revenue expected to rise from 107.2 billion euros in 2019 to 408.7 billion euros by 2030 [3].

The IoT domain is rapidly expanding in scale; however, along with this growth, there are increasing challenges related to security and data privacy. Cyberattacks targeting IoT devices have surged significantly, with millions of incidents reported annually. In 2016, the cybersecurity landscape was significantly affected by the Mirai botnet attack [4]. This attack strategically targets unsecured IoT devices by scanning a vast array of devices, including digital cameras, in search of open telnet ports. Subsequently, attackers attempted to gain access using default passwords. By successfully infiltrating these vulnerable devices, they effectively constructed a botnet and subsequently unleashed Distributed Denial of Service (DDoS) attacks. In 2022 alone, there were over 112 million IoT attacks worldwide, a stark increase compared to the approximately 32 million detected cases in 2018 [5]. Addressing the security challenges is crucial for ensuring the continued growth and success of the IoT.

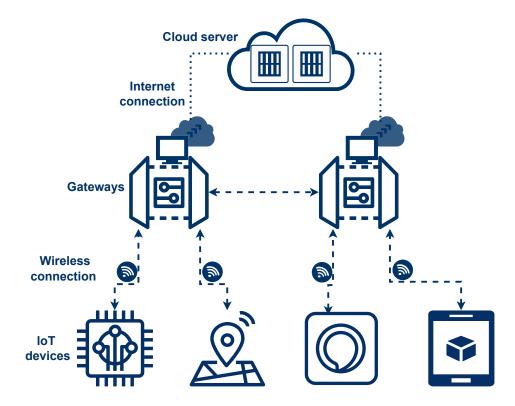

The IoT environment's architecture is significant as highlighted in Figure 1.1, spanning

from the top where cloud servers manage vast amounts of data to the bottom, housing IoT gateways that collect data from devices. IoT protocols enable wireless connections between the gateways and devices. Finally, IoT devices, which are physical components, interact with the real world. IoT end-devices are a subset of IoT devices that possess limited resources in terms of performance, computing capabilities, memory capacity, and power consumption. The security of embedded systems within IoT end-devices has been targeted through various mechanisms. This can be addressed using several measures such as protecting physical access to devices, securing data privacy with cryptographic encryption, and enhancing communication security. Embedded systems in IoT devices now possess built-in communication capabilities, which serve as the primary entrance for data to the IoT network.

Figure 1.1 – IoT Environment Architecture

The built-in wireless communication capability is a significant entry point for security threats to IoT devices. It represents a crucial attack surface housing various vulnerabilities that attackers exploit to launch cyberattacks in the IoT environment. As an illustrative example, Forescout Research Labs uncovered 33 vulnerabilities, collectively referred to as AMNESIA:33 [6,7]. These vulnerabilities pose a significant risk to millions of IoT devices

and affect four open-source TCP/IP IoT stacks. These vulnerabilities primarily result in memory corruption, giving attackers the ability to compromise devices, gain remote control, execute malicious code, initiate denial-of-service attacks, and steal data. Attackers can then potentially access various environments where these devices are deployed, often owing to common oversight during software development and product design phases, where security considerations are neglected. The emergence of high-performance, low-cost platforms and associated software [8] has also expanded the opportunities for attackers and simplified their access to the lower layers of communication networks. The potential economic situations of these vulnerabilities are considerable, given that open-source IoT stacks are widely utilized by numerous vendors in their products. Addressing these vulnerabilities requires the deployment of patches across millions of IoT devices. However, a challenging aspect of this situation is that some IoT devices cannot be patched due to technical unfeasibility.

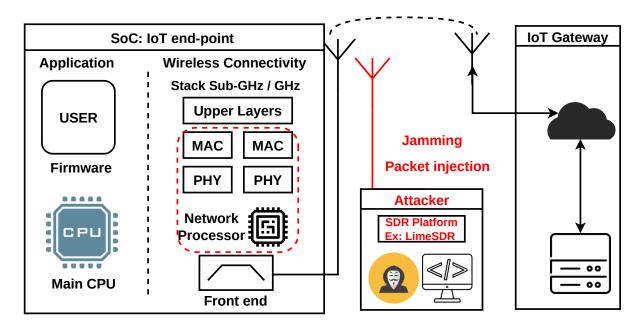

In this thesis, we address the security challenges presented by IoT end-devices, with a particular emphasis on security threats affecting their wireless connectivity. The primary objective is to provide a robust security mechanism capable of detecting potential attacks.

### 1.2 Motivation

Embedded Systems on Chip (SoCs) in IoT end-devices include security mechanisms against cyberattacks, such as cryptographic accelerators for data encryption, secure boot procedures, and over-the-air update mechanisms. These are crucial for addressing the IoT device security challenges. However, IoT end-devices lack monitoring and detection mechanisms that can track system metrics and analyze behavior to identify malicious activities. Combining monitoring and detection with existing security measures can enhance the resilience of IoT devices to security challenges.

The attack surface of IoT end-devices has expanded significantly owing to their wire-less connectivity. For example, jamming attacks disrupt IoT communication protocols, leading to Denial of Service (DoS) incidents. These attacks can present difficulties in countering them using existing protections and necessitate monitoring network metrics, such as Received Signal Strength Indicator (RSSI) and Signal Noise Ratio (SNR), to detect jammers. Another type of cyberattack involves packet injection, which exploits software-memory vulnerabilities. These attacks range from simple DoS attacks to the control of IoT devices. Protection against such attacks often requires access to IoT de-

vices for software patching or updates. Real-time monitoring and detection mechanisms can help to identify these vulnerabilities. However, implementing monitoring and detection security mechanisms in resource-constrained embedded IoT systems presents several challenges. The development of lightweight monitoring and detection methods against wireless attacks is promising for mitigating these issues.

## 1.3 Contributions and Organization of Manuscript

#### 1.3.1 Contributions

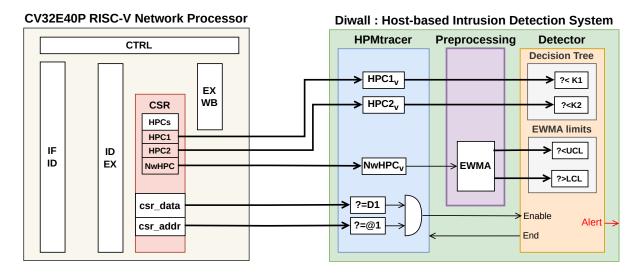

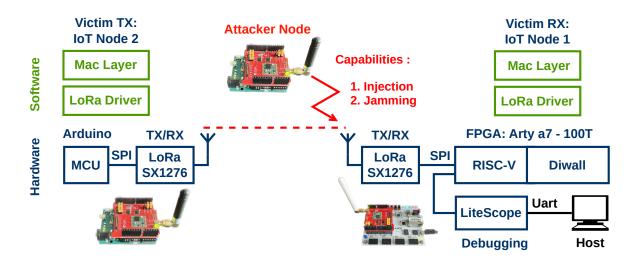

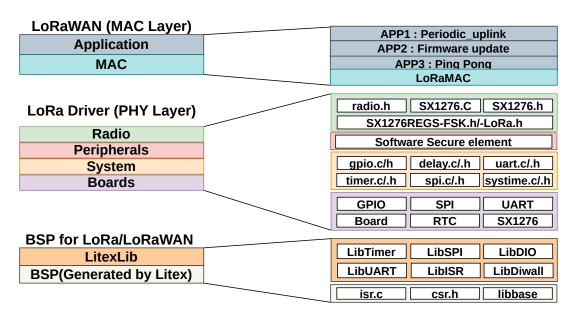

This thesis comprises two significant contributions. It introduces a methodology and the associated experimental framework for simulating, emulating, and implementing wireless attacks, such as jamming and packet injection. This approach also includes dataset generation for microarchitectural and network metrics, which are essential for constructing a Host-Based Intrusion Detection System (HIDS) tailored for IoT end-devices. In addition, it introduces a lightweight IDS called *Diwall*. It was designed to detect packet injection and jamming attacks by monitoring microarchitectural events and RSSI metadata within the LoRaWAN stack.

In our first contribution, we introduce our methodology and the associated framework to study packet injection and jamming attacks that target IoT protocol stacks. This framework generates extensive datasets for both the simulated and real-world scenarios. We delve into the behavior of microarchitectural events during memory stack and heap buffer overflows, focusing on packet injection attacks. Additionally, we examined network metadata metrics such as RSSI and SNR to identify jamming attacks. Our research encompasses machine learning and statistical techniques applied to the generated datasets. Importantly, this comprehensive framework is adaptable for use with various IoT protocol stacks and Instruction Set Architecture (ISA) processors. This adaptability is possible because monitored microarchitectural and RSSI metadata are present in modern Central Processing Units (CPUs) and IoT protocol stacks. Within this methodology, we employ a simplified Media Access Control (MAC) layer that can be substituted with more complex MAC layers that we demonstrated using the LoRaWAN MAC layer. Similarly, the LoRa Physical (PHY) layer can be replaced with technologies such as Bluetooth or Zigbee to investigate the same wireless attacks that pose threats to the mentioned IoT stacks.

In our second contribution, we introduced *Diwall*, a hardware-based lightweight HIDS

that requires minimal software instructions for configuration and control. *Diwall* uses microarchitectural event analysis to identify packet injection attacks that exploit buffer overflow, and it utilizes RSSI metrics to detect jamming attacks. We implemented *Diwall* as a compact component within a RISC-V processor on an Field Programmable Gate Array (FPGA) board. In real-world scenarios, we evaluated the detection rates and achieved impressive levels of approximately 99.98%. Moreover, *Diwall* requires a minimal FPGA area overhead of approximately 14.30%, consuming 22.89% of LUTs and FFs, and does not negatively impact system performance.

#### 1.3.2 Organization

The remainder of this manuscript is organized as follows.

Chapter 2: This chapter aims to establish a comprehensive background on security threats and mechanisms applied in SoC for Low-Power and Low-Data-Rate IoT end-devices. We begin by providing an overview of SoCs in both research and industry contexts. Subsequently, we delve into the security aspects of the SoC wireless connectivity for the considered waveforms. We also discuss the implementation approach with respect to the attack surface. In this chapter, we explore the potential of using intrusion detection for IoT end-devices, including related works, identified challenges, and requirements.

Chapter 3: In this chapter, we detail the methodology used in our framework to build Diwall, a lightweight HIDS designed for detecting attacks in the wireless connectivity of IoT end-devices. We outline the targeted threat model, our proposed approach, and the key features of Diwall in the context of related works. Furthermore, we investigate wireless attacks, jamming, and packet injection based on memory corruption in separate sections. For packet injection attacks, we utilize microarchitectural event datasets generated from simulations and apply machine learning classification techniques. Another section focuses on network metadata metrics, such as RSSI and SNR, in real communication scenarios, studying their use in detecting jamming attacks through statistical techniques. We also discuss the machine learning classification and statistical techniques used for the generation of Diwall detection models.

Chapter 4: In this chapter, we present the implementation details of *Diwall* on hardware using detection models for packet injection and jamming attacks. We elaborate on the detection models generated using the framework outlined in the previous chapter. Additionally, we provide insights into the *Diwall* architecture, configuration, resource utilization, and its impact on FPGA performance. We evaluate its detection rates and

present a practical use case of *Diwall* within a real IoT protocol stack.

Chapter 5: The final chapter is dedicated to concluding remarks on the obtained results, identifying limitations, and discussing the challenges encountered in this thesis. We also explore future research perspectives, address the limitations, and suggest potential improvements.

# SYSTEM-ON-CHIP FOR IOT AND WIRELESS SECURITY

#### Introduction

This chapter covers background knowledge for understanding an SoC in the IoT domain. First, it provides an overview of the SoC subsystems for low-power, low-data-rate IoT end-devices. In addition, an identification and comparison of several features are described for SoCs used in industry and those used in research. Second, a focus is proposed on the principal wireless connectivity subsystem architectures for the low-power, low-data-rate waveforms considered in this study. Based on this knowledge, we highlight the security issues related to wireless connectivity, including existing vulnerabilities, attacks, and the proposed security mechanisms. Finally, this chapter addresses the potential of IoT intrusion detection systems as a security mechanism and the associated challenges. A concluding section is provided based on the lessons derived from the literature.

#### 2.1 SoC for Low-Power and Low-Data-Rate End-Devices

#### 2.1.1 SoC Overview

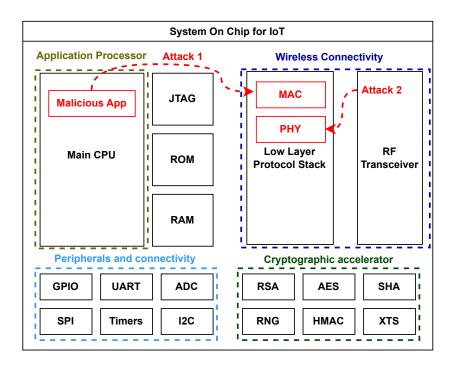

IoT SoCs are an integrated circuit designed to offer both processing and communication capabilities. To achieve this, various modules and subsystems were integrated. Figure 2.1 shows a general overview of the subsystems inside an SoC system.

SoC subsystems can be classified into four main categories according to their characteristics:

- **Application processor:** Generic CPU that hosts the firmware of the user.

- **Peripherals and connectivity:** It includes general-purpose inputs and outputs (GPIOs) and various communication front ends, such as UART, SPI and I2C,....

They are used to interconnect the SoC with external modules and sensors. Hardware timers are also included.

- Cryptographic accelerator: An SoC is provided with the necessary dedicated hardware for implementing cryptographic algorithms, such as AES, RSA and SHA,....

- Wireless connectivity: An SoC incorporates modules designed to implement and process the lower layers of IoT protocol stacks (MAC and PHY layers). It also contains a built-in Radio Frequency (RF) transceiver.

Figure 2.1 – Block Diagram of SoC for IoT end-devices

## 2.1.2 SoC in Industry

Many chip manufacturers in the industry introduced SoC solutions [9–11] for IoT a few years ago, in which wireless capabilities were built-in. Such SoCs integrate all the major components featured in Figure 2.1 on one chip. They provide a range of integrated network connectivity technologies, mainly commonly used IoT protocols, such as LoRaWAN, Bluetooth/Bluetooth Low Energy (BLE), and ZigBee. The built-in radio ensures dedicated wireless network access, removing the problem of compatibility issues.

They also reduce implementation costs, energy requirements, and complexity compared to traditional SoCs, requiring expensive hardware for wireless connectivity.

In industry, several SoCs feature built-in wireless connectivity. Here, we discuss only three types of SoCs designed with multi-protocol capabilities.

ESP32-H2 [11] is an SoC developed by Espressif Systems and is part of the ESP32 series. The SoC is powered by a single-core, 32-bit RISC-V processor. The Wireless connectivity supports the coexistence of radio protocols in the 2.4 GHz band, with each protocol having its own Application Specific Integrated Circuit (ASIC) baseband. Achieving a more flexible approach of wireless connectivity and adaptability when protocols need to be changed involves the integration of a dedicated network CPU. STM32WL55CC [9] is a STMicroelectronics SoC, which is part of the STM32WL series. It combines an Arm Cortex-M4 processor core as the main CPU and an Arm Cortex-M0+ core dedicated to sub-GHz wireless connectivity. It supports various sub-GHz IoT stacks and proprietary protocols. CC1352R [10], produced by Texas Instruments, features a multiband device specifically tailored for IoT and proprietary protocols in the sub-GHz and 2.4GHz frequencies. SoC CC1352R incorporates dual Arm Cortex-M4F/M0 cores, supporting a variety of protocol operations. Wireless connectivity is managed by an Arm Cortex-M0 core and has the ability to manage simultaneous protocols.

Security functions are provided by most chip manufacturers for their SoCs, typically using modules that provide similar security functions. ESP32-H2, STM32WL55CC, and CC1352R incorporate hardware security features, such as cryptographic acceleration (AES, SHA, RSA, and TRNG). Integrated hardware enables code authentication for a wide range of security services. These include secure boots, secure firmware update mechanisms, memory encryption/decryption, and protocol stack key generation.

Table 2.1 provides a summary of the three industry IoT SoCs discussed. The main focus of the comparison was wireless connectivity capabilities. Further details are provided in technical datasheets [9–11].

#### 2.1.3 SoC in Research

Researchers and the open-source community have been involved in the development of various SoCs in different HDL languages [12,13]. These SoCs are commonly designed to be highly scalable, allowing new functionalities to be added according to the specific requirements of the application. A significant number of these SoCs are based on the RISC-V architecture, an open-source ISA [14,15]. The current focus in research-oriented

| Features                 | CC1352R [10]   | STM35WL55 [9]            | ESP32-H2 [11]        |

|--------------------------|----------------|--------------------------|----------------------|

| Main CPU                 | Cortex M4F     | Cortex M4 or M0+         | 32 bits RISC-V       |

| Wireless connectivity    | Cortex M0      | Cortex $M0+$ or $M4$     | ASIC Baseband        |

| Frequency Band           | 2.4 + sub-GHz  | $\operatorname{sub-GHz}$ | $2.4\mathrm{GHz}$    |

| Concurrent Multiprotocol | $\checkmark$   | X                        | X                    |

| Radio Flexibility        | $\checkmark$   | ✓                        | X                    |

| Radio/App Isolation      | $\checkmark$   | ✓                        | X                    |

| Main Security            | Secure Boot/Fi | irmware update/Crypto    | ography Acceleration |

Table 2.1 – Industrial IoT SoCs Features Comparison

SoCs is often on separate subsystems within the SoC, such as the processor architecture and peripheral subsystems. Hardware-based security accelerators or built-in mechanisms have also been discussed and proposed as separate subsystems [16, 17]. Some processors have been modified with ISA extensions [18] to incorporate instructions dedicated to specific tasks such as security or DSP. However, open-source platforms do not always offer wireless connectivity. They provide a multipurpose and highly flexible SoC that can be customized and expanded. Our discussion here is specifically centered on RISC-V-based SoCs. The reasons for this focus are the open-source nature of RISC-V and the extensive involvement of the community in both research and industrial applications.

The PULP (Parallel Ultra-Low Power) platform project [13] covers open-source SoC designs for energy-efficient computing. It provides multicore support and multiple IP cores for peripherals, such as UART, SPI, JTAG, and I2C. In addition, PULP supports the integration of hardware accelerators. The PULP SoC uses 32-bit RISC-V processors and can be configured to use either a 4-stage RI5CY pipeline [19] or 2-stage Zero-riscy pipeline [20]. Several SoCs optimized for different use cases are based on the PULP platform, such as PULPissimo [21] and PULPino [15], designed for IoT applications at the edge. They are available for RTL simulation, FPGA implementation, and ASICs. The CORE-V-MCU [14] is a modern 32-bit RISC-V-based open-source SoC for IoT devices. It was originally based on the PULP platform and has the same peripherals as the PULPissimo SoC. However, it has been extended to include an eFPGA to implement customs peripherals to improve the energy efficiency of the SoC.

LiteX [12] is an SoC building framework that provides a wide range of open-source components. It includes buses, simple IPs such as RAM and UART, complex IPs, and supports for various CPUs and ISAs. The framework supports mixed HDL integration

and compatibility with VHDL, Verilog, System Verilog, Migen, Spinal HDL, . . . . Taking advantage of LiteX's vast collection of open-source IPs and support for mixed HDLs, the design, simulation, and implementation of a custom SoC for FPGA boards are simplified with respect to the PULP platform [13].

Table 2.2 provides a comparable overview of available SoCs. It concentrates primarily on the open-source cores and peripherals included, CPU and ISA supported, and simulation and prototyping flows. Further details can be found in [12–15].

| Features      | PUPLino [15]   | PULP [13]            | CORE-V-MCU [14]    | LiteX Framework [12] |

|---------------|----------------|----------------------|--------------------|----------------------|

| CPU           | RI5CY/Zero     | o-riscy              | CV32E40P+ eFPGA    | Various CPUs/ISAs    |

| Core Numbers  | Single         | m Multi              | Single             | Multi/Single         |

| Peripherals   | UART, SPI, I2C | UART, S              | PI, I2C, CPI, JTAG | Simple + Complex IPs |

| BUS           | APB + AXI4     | $\mu { m DM} A$      | A+TCDMI+APB        | Whishbone/AXI        |

| Cache $L1/L2$ | X              | ✓                    | ✓                  | ✓                    |

| HDL support   |                | Mixed HDL            |                    |                      |

| Prototyping   | RTL S          | RTL Simulation, FPGA |                    |                      |

Table 2.2 – Comparison of Research SoCs Features

This section delves into the discussion of SoCs in both research and industry contexts. Additionally, we provide a concise overview of the SoC subsystems. Shifting our focus to the next section, we delve into various implementation approaches for wireless connectivity, with a specific emphasis on the considered IoT protocol stacks.

## 2.2 SoC Wireless Connectivity

#### 2.2.1 IoT Protocol Stack

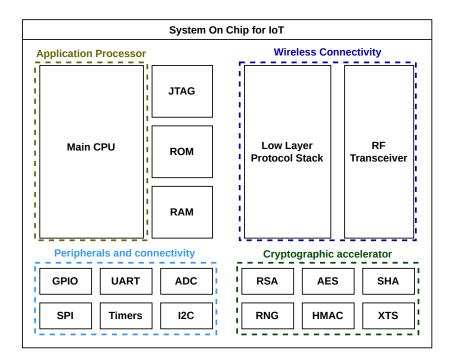

There are several main layers in an IoT protocol stack. First, the PHY layer manages modulation and demodulation, the physical transmission of data, and is used to establish connectivity physically. Another important layer is the MAC layer, where network packets are processed. It handles access to the physical medium and ensures that network packets are transmitted and received according to the standards. In addition to the MAC layer, there are additional upper layers for the application-specific protocols. They manage the requirements specific to different IoT applications. They provide the functionality required for data exchange and interaction with the user applications. IoT SoC wireless connectivity generally includes a physical layer and MAC layer.

Figure 2.2 presents a typical block diagram of an IoT protocol stack along with three other protocol stacks: BLE, LoRaWAN, and ZigBee. An IoT protocol can generally be considered to have three main levels: the physical, MAC, and application layers.

Figure 2.2 – IoT Stack Layers

#### 2.2.2 Considered Waveforms

The focus of this research is on low-power IoT protocols that support low-data-rate. Targeting specific IoT end-devices with power constraints, IoT stack technologies are explored for implementation in low-power wide area networks (LPWANs) operating in the sub-GHz frequency bands. An example of such technology is LoRaWAN. In addition, low-data-rate protocols that operate in the 2.4 GHz frequency band, such as BLE and ZigBee, have also been studied.

LoRaWAN: LoRaWAN, or long-range wide-area network, is a MAC protocol designed for managing wireless communication between battery-powered IoT end-devices and gate-ways within a large-scale network [22]. This protocol forms a software layer that prescribes the interaction between the devices and the LoRa hardware. Built on top of the sub-GHz band LoRa physical layer [23], LoRaWAN is well suited for transmitting small payloads such as sensor data over extended distances. The key feature of LoRaWAN is its utilization of a 'star-of-stars' topology [24]. In this configuration, end-devices constitute a star pattern around the gateways, which then communicates with a central network server, generating another star pattern. This hierarchical structure facilitates long-range

communication while minimizing power consumption because each end-device communicates only with a proximate gateway rather than the central server. Moreover, gateways can be strategically positioned at elevated locations with broad coverage to optimize the range of communication. Therefore, LoRaWAN has emerged as an efficient solution for wide area networks (WANs), rendering it particularly applicable to use cases such as IoT applications.

BLE: BLE, or Bluetooth Low Energy, is an energy-efficient variant of traditional Bluetooth technology, it was first introduced as part of Bluetooth 4.0, in 2010 [25]. Tailored explicitly for IoT applications, BLE has been widely adopted in various sectors, such as smart homes, healthcare, and industrial automation, primarily because of its power efficiency and design tailored for short-range communications. Uniquely, BLE operates using a star topology, where a central 'master' device forms connections with multiple 'slave' devices. This master device is capable of sending and receiving data from any of its connected slave devices, but communication between the slave devices is not possible. This specific network structure provides an effective power management strategy because the slave devices can remain in sleep mode until the master initiates a connection. Such power conservation capabilities make BLE particularly suited for IoT devices that require extended operational periods for battery power.

**ZigBee:** ZigBee, a high-level wireless communication protocol, was purposefully designed for short-range, low-power communications [26]. Built upon the MAC and Physical layers of the IEEE 802.15.4 standard for wireless personal networks [27], it has a distinct topology adaptable to multiple network structures, such as mesh, star, and tree topologies. This distinct characteristic affords ZigBee with high resilience and network robustness, as it can reroute data through alternative paths if a node fails or a connection is lost. Moreover, ZigBee's various topological supports enhance its demand for diverse IoT applications. Uniquely, while ZigBee operates in the 2.4GHz band like Bluetooth, it is also optimized to function in the sub-GHz range in specific geographical regions, thereby expanding its usability.

#### 2.2.3 Network Processor Architectures

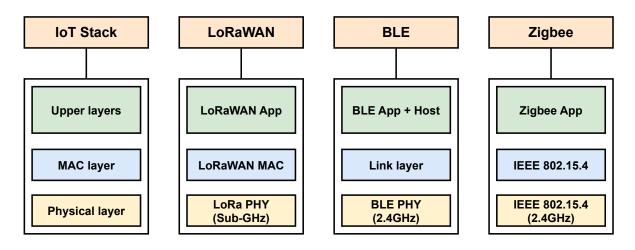

In SoC architecture, wireless connectivity systems typically include a network processor to manage the PHY and MAC layers. To achieve these requirements, a range of

technologies, such as CPUs, FPGAs, and dedicated ASICs, are often used. The MAC layer can be implemented in software or hardware, whereas, for each protocol, a dedicated ASIC module is typically used to implement the PHY layer.

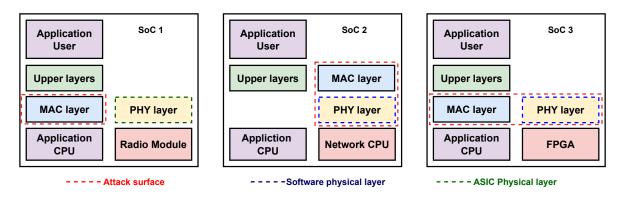

However, to improve the flexibility of wireless connectivity, it has recently been shown that the PHY layer can be implemented in software [28–31]. Figure 2.3 summarizes the implementation approaches and technologies for SoCs with wireless connectivity. In this figure, we present three distinct methods of implementing wireless connectivity. In SoC 1, the PHY layer is implemented using dedicated hardware specific to each protocol. Conversely, in SoCs 2 and 3, it is implemented using software through Software Defined Radio (SDR), leveraging diverse technologies, including FPGA and CPU. The SDR approach

Figure 2.3 – Wireless Connectivity SoC Technologies

has the advantage of being reconfigurable and adaptable to a variety of protocols. Many SoCs with wireless capabilities support multiple protocols. The use of SDR for baseband digital processing is of interest to many researchers. It has inspired the development and implementation of a multitude of architectural approaches, each with its own particular strategies.

Using Hybrid FPGA: In [32], the authors demonstrated the implementation of an SoC with wireless connectivity, where the PHY layer is based on SDR technology. This platform, intended for Over the Air (OTA) programmable IoT devices, uses a Lattice FPGA and a 32-bit Cortex M4F Microcontroller Unit (MCU). The use of such hybrid systems (FPGA and/or MCU) in constrained IoT devices offers significant advantages in terms of computing performance and flexibility. However, these advantages do not extend to energy consumption, and this type of system is less efficient than dedicated hardware or low-power microcontrollers.

Using Dedicated CPU Architecture: The deployment of an SDR PHY layer on a dedicated architecture has become increasingly appealing owing to its consideration of the power consumption. For instance, the authors of [28] proposed an SDR baseband processor for IoT SoCs. This solution, based on a custom Single Instruction Multiple Data (SIMD) datapath, only consumes  $1.3\ mW$  of power. Alternatively, another approach [29] introduced a scalar datapath in a baseband processor for IoT SoCs, focusing on low power consumption. It achieved an impressive average energy consumption rate of  $2.41\ nJ/cycle$  when operating at  $3\ MHz$ . While these dedicated architectures for SDR implementation effectively minimize power consumption, they require IoT protocols' waveform algorithms to be specifically coded in the assembly language for each dedicated processor. Moreover, these architectures lack the ability to utilize existing DSP libraries, such as ARM CMSIS DSP, which curtails their programmability.

Using Extended Generic CPU Architecture: Numerous studies have demonstrated the feasibility of using a generic CPU with ISA extensions for the SDR. The authors of [30] suggested adding DSP extensions to the RISC-V ISA. These extensions are implemented on a 32-bit processor with RV32IM for integer multiplication and division. This setup provides significant flexibility and ultra-low-power consumption. Demonstrations showed a potential power consumption of 380  $\mu$ W for Bluetooth LE demodulation and 225  $\mu$ W for LoRa preamble detection.

Another study [31] focused on an ultra-low-power SoC architecture. It uses an ARM Cortex-M4 processor with SIMD or DSP extensions for protocol-specific computations. It also utilizes a hardware digital front end for generic signal processing. The proposed architecture was prototyped using 28 nm FDSOI. The PHY layers of LoRa and Sigfox protocols were implemented in the software, resulting in sub-milliwatt power consumption  $(32-332~\mu W)$ .

Table 2.3 presents a comparison of the wireless connectivity of IoT SoCs using SDR baseband processor architectures and their features. Architectures are compared based on their capability to run more than one protocol at the same time and their programmability based on the difficulty required to develop waveforms. Orders of magnitude for the dynamic power for each type of architecture were also proposed. More details can be found in [28–32].

Utilizing generic CPU architectures for baseband processors in an SDR is promising. This is because of their flexibility, programmability, and power efficiency. However, during

| Architecture    | Hybrid FPGA [32] | CPU (dedicated) [28,29] | CPU (extended) [30,31] |

|-----------------|------------------|-------------------------|------------------------|

| Multi Protocol  | ✓                | X                       | X                      |

| Programmability | +                | +                       | +++                    |

| Flexibility     | +++              | ++                      | ++                     |

| Dynamic power   | $\sim 300~mW$    | $\sim 2~mW$             | $\sim 0.5~mW$          |

| Prototyping     | ASIC             | FPGA                    | FPGA [30], ASIC [31]   |

Table 2.3 – Comparison of Network Processor Architectures in Research

the design phase, challenges, such as ensuring security against traditional vulnerabilities for wireless connectivity, need to be addressed. The use of SDR in wireless connectivity makes the software part of an IoT stack more extensive. The expansion of software enhances its flexibility and supports multiple protocols. However, this can increase the number of SoC attack surfaces, as illustrated in Figure 2.3. Consequently, it may increase the vulnerability to security threats. In the next section, security threats related to wireless connectivity are explored, including their points of entry, potential vulnerabilities and attacks, and the associated countermeasures.

## 2.3 Security of SoC Wireless Connectivity

IoT end-devices, in which wireless capabilities are potentially vulnerable, face a significant attack. This section details the common vulnerabilities and attacks on low-data-rate, low-power waveforms/protocols. This also includes an assessment of the attack model. In addition, it explores the security mechanisms discovered during the literature review. This section concludes with security recommendations for IoT devices.

## 2.3.1 Attack Entry Points

SoCs in IoT devices can have multiple points that are susceptible to attack. In Figure 2.4, we highlight only two potential entry points. One entry point could stem from the application processor executing a malicious process that attempts to carry out illegitimate actions, such as launching a DDoS attack [4]. In such attacks, numerous IoT devices are exploited to overwhelm servers collectively. The second potential entry point relates to the vulnerabilities present in the lower layers of the protocol stacks. Our research primarily focuses on this entry point, specifically, the wireless connectivity of SoCs.

Figure 2.4 – IoT SoC Attacks Entry Points

#### 2.3.2 Vulnerabilities

Several vulnerabilities in IoT devices have recently been identified. Vulnerabilities are found in the communication elements of the devices. They affect several protocols. These include TCP/IP, LoRaWAN, ZigBee, and BLE,.... Numerous vulnerabilities are often associated with the implementation of the protocol standards. However, others are specific to the standard itself.

AMNESIA:33 The Forescout Research Labs conducted a security study on the TCP/IP stacks [7]. They published a report analyzing seven open-source TCP/IP stacks. They found 33 new critical vulnerabilities in four stacks: uIP, FNET, picoTCP, and Nut/Net. These stacks are heavily used in millions of IoT devices and by more than 150 vendors. Many of these vulnerabilities are traced back to poor software development practices in the operating systems. These practices include neglecting the basic input validation in SoCs, embedded devices, networking equipment, and various IoT devices for enterprise and consumer use. The exploitation of these vulnerabilities, referred to as AMNESIA33, can result in remote control by attackers. This can occur through memory corruption (buffer overflow) in IoT devices. These risks include compromised devices, execution of

malicious code, DoS attacks, and sensitive information theft. The authors of AMNE-SIA:33 acknowledge that identifying and rectifying these vulnerabilities pose a significant challenge to the security community. In response, they proposed mitigation measures for AMNESIA33. These include implementing solutions that provide granular visibility of devices through network communication monitoring. They also recommend isolating devices or network segments that are vulnerable to these threats to manage potential risks.

BLEEDINGBIT is a significant vulnerability of BLE chips [33]. It impacts access points from the Cisco, Meraki, and Aruba solutions. These access points use a Texas Instruments (TI) BLE chip. This vulnerability allows an unauthenticated attacker to execute code remotely on targeted chips. This issue, referred to as CVE-2018-16986, originates from a masking error. This error can lead to remote code execution in the BLE stack of the TI chip. This is caused by a memory corruption bug during the parsing of BLE advertising packets. Bluetooth's specifications changed from version 4.2 to 5.0. This change allows larger advertising packets. The size limit ranged from 37 bytes in version 4.2 to 255 bytes in version 5.0. Upgrading a BLE stack from version 4.2 to 5.0 can cause bugs due to this change. A specific problem can occur if a developer does not hide the Reserved for Future Use (RFU) bits. They must do this when writing the code to parse the packet header length field. The RFU bits were 2 in version 4.2 and decreased to 1 in version 5.0. This vulnerability was identified in the BLE stack of the Texas Instruments CC26xx chip family.

Another vulnerability, CVE-2018-7080, was found in the Texas Instruments BLE stack SDK. This vulnerability involves OTA firmware download (OAD), on the affected device, provided its BLE is turned on, without any other prerequisites or knowledge about the device. First, the attacker sends multiple benign BLE broadcast messages, called "advertising packets," which will be stored in the memory of the vulnerable BLE chip in targeted device. While the packets are not harmful, they contain code that will be invoked by the attacker later on. This activity will be undetected by traditional security mechanisms of TI's BLE stack SDK. The Aruba 300 Series access point uses TI's OAD and CC2540 chips to update firmware. However, this allows a nearby attacker to access the device and install malware.

LoRaDawn The Tencent Blade team discovered two vulnerabilities in LoRaWAN, CVE-2020-11068 and CVE-2020-4060 [34]. These vulnerabilities can cause a remote DoS on LoRaWAN end-devices and potentially enable Remote Code Execution (RCE) on the LoRaWAN gateway under certain conditions. CVE-2020-11068 was found in the LoRaWAN end-device stack implementation, specifically in versions of the LoRaMac-node below V4.4.4. This issue arises during the OTA Activation (OTAA) process and involves a reception buffer overflow condition. This can occur when the size of the received data remains unchecked.

In contrast, CVE-2020-4060 is a Use-after-free (UAF) vulnerability. This leads to memory corruption on 32-bit machines and was found in the LoRaWAN Gateway implementation, specifically the LoRa Basics<sup>TM</sup> Station. This station uses a Configuration and Update Server (CUPS) protocol to check for updates. The UAF issue occurs when the signature length of a message from a CUPS server exceeds 2 GBytes.

#### 2.3.3 Attacks

Many attacks exploit vulnerabilities in IoT network protocol stacks [35, 36]. These can affect service availability, data integrity, and confidentiality. Attackers can exploit vulnerabilities in the lower layers of a protocol stack This includes the MAC layer or the physical layer. Attackers can introduce malicious network packets to target victims or jam their communication channel, resulting in exploits as DoS, Man in the Midlle (MITM), and RCE attacks.

Table 2.4 provides a comparison of reported attacks on various protocols. It focuses on LoRaWAN, a sub-GHz protocol, and 2.4 GHz protocols like Bluetooth, BLE, and ZigBee. The comparison is based on the targeted protocols, exploited and targeted layers in the IoT protocol stack, as well as the used vulnerabilities and their exploits.

In the following paragraphs, we provide detailed explanations of packet injection and jamming wireless attacks.

Packet Injection: An attacker, typically an unauthorized entity, introduces malicious packets into the target device or its communication pathway. Through packet injection attacks, the attacker aims to inject false data, take over legitimate device roles, and disrupt the network availability. Such attacks can pave the way for more advanced exploits including RCE and MITM attacks. Within the LoRaWAN structure, an attacker might position himself between a gateway and an IoT device, impersonating either the end-device

Table 2.4 – Security State-of-the-Art IoT Low Data-Rate Protocols (LoRaWAN, ZigBee, BLE)

| Attack                 | Protocol | РНҮ          | MAC | UL  | Vulnerability      | Exploit        |

|------------------------|----------|--------------|-----|-----|--------------------|----------------|

| Wazabee [37]           | ZigBee   | Е            | E/T | Т   | BLE API            | DoS, injection |

| Selective Jamming [35] | LoRaWAN  | $\mathbf{E}$ | E/T | Τ   | Header plain-text  | DoS, Wormhole  |

| Spoofing [38]          | LoRaWAN  | $\mathbf{E}$ | E/T | -   | Authentication     | DoS            |

| Rescuing [39]          | LoRaWAN  | -            | T   | Τ   | Protocol weakness  | Replay, DoS    |

| InjectBLE [40]         | BLE      | $\mathbf{E}$ | E/T | Τ   | Pairing            | MITM, Sniffing |

| Downgrade [36]         | BLE      | -            | -   | Τ   | Design flaws       | DoS, MITM      |

| Injection-free [41]    | BLE      | -            | -   | E/T | Limited Bounding   | DoS, MITM      |

| Downgrade [42]         | BT/BLE   | -            | E/T | E/T | Insecure BLE clock | x MITM         |

T (targeted layer), E (Exploited layer), UL (Upper layers).

or presenting a false gateway. Flooding the LoRaWAN environment with excessive data can trigger several exploits; for example deny service to legitimate devices, and because LoRaWAN operates in a low-power context, constant receiving or transmitting can lead to rapid battery reduction.

Prior studies have highlighted the viability of various exploits associated with packet injection attacks in IoT protocols. The chirpOTLE framework, designed for evaluating LoRaWAN security, is detailed in [38]. The tool provided allows the reproduction of various LoRaWAN attacks that affect its availability and integrity, including wormhole and replay attacks. This involves capturing and retransmitting data packets using two LoRa transceivers. The first transceiver, acting as an entry node, is positioned near the target End Device (ED), while the second transceiver, functioning as an exit node, is situated close to the gateway (GW). When the entry node captures a complete LoRa frame, it sends it to the exit node via an out-of-band channel, which then replays the message for the GW to process. In this setup, the attacker can modify the message metadata, especially by introducing incorrect data regarding the timing, location, SNR, and RSSI values. The security protocol of LoRaWAN 1.0, as thoroughly analyzed in [39], exhibits multiple vulnerabilities. The authors delved into attacks on LoRaWAN that compromise data integrity, confidentiality, and network availability. Highlighted attacks capture LoRaWAN's join procedure frames and subsequently execute exploits, including desynchronization of legitimate end-devices, replay attacks, and frame decryption.

Attacks similar to those found in LoRaWAN also plague Bluetooth, BLE, and ZigBee

stacks. The authors of [40] introduced InjectBLE, an attack that can insert arbitrary frames into a pre-established BLE connection. This can lead to various exploits, such as the hijacking of master-slave roles and MITM attacks. InjectBLE leverages a feature in the BLE specification that allows devices to adjust their reception windows to account for clock inaccuracies. By exploiting this, InjectBLE carries out a race-condition attack, permitting an attacker to inject a frame at the start of the reception window. This vulnerability exists inherently in the BLE specification, regardless of how the stack is implemented. In [37], the same authors introduce the "wazabee" attack, which manipulates the radio device within a BLE chip to transmit and receive 802.15.4 frames, specifically ZigBee frames. This exploitation hinges on the similarities between the physical layers, notably the GFSK and O-QPSK modulations utilized by both the BLE and ZigBee protocols. In [41], researchers pointed out a vulnerability in the BLE stack implementation linked to its bonding list—a storage mechanism for cryptographic keys from prior bonded devices. When this list is full and a new bond request is made, the existing key is replaced, affecting its associated device. Attackers can exploit this by injecting packets from a new device and filling up the list, prompting the BLE device to discard all legitimate keys and forcing genuine devices to rebond. Some BLE versions, when faced with a full list, may decline new bonds or permit insecure connections, opening up potential security risks, including DoS attacks.

Packet injection attacks often exploit vulnerabilities found in the lower layers of IoT protocol stacks. These vulnerabilities may arise from the protocol's specifications or implementation.

Jamming: Jamming is a significant security concern for IoT networks. Even systems with robust high-level security can be compromised. Essentially, jamming disrupts wireless signals, either intentionally, as with radio frequency interference, or unintentionally, from noise and receiver collisions. The aim of the jammer is to dominate the channel and block legitimate nodes. There are two main types of jamming: continuous and triggered [43]. During continuous jamming, the attacker persistently interferes with the channel. In triggered jamming, interference occurs only upon meeting specific conditions such as preamble detection.

Recent studies, such as those referenced in [44,45], have highlighted the vulnerability of IoT protocols such as BLE, ZigBee, and LoRaWAN to jamming. The rise of affordable SDR platforms, coupled with open-source software, such as [8], facilitates access to

frequency ranges used by BLE and LoRaWAN. A refined jamming technique, known as selective jamming, has emerged. Here, the jammer disrupts communication after decoding the MAC header and end-device address. This precise attack can isolate and block a specific device in an IoT environment without affecting the other network devices.

The study in [35] showcases selective jamming attacks that target LoRa and LoRaWAN transmissions. The vulnerability arises from the protocol's extended packet air time, giving attackers ample opportunities to detect specific messages and emit jamming signals during the broadcast of the original message. A similar threat exists in BLE stacks. As noted in [46], researchers have created a selective jammer for BLE advertising using affordable, readily available hardware. The jammer can target specific beacons with unique device addresses. Given that BLE beacons operate on various advertisement channels, the designed jammer includes a discovery component that scans all channels and identifies those in use using targeted beacon sources.

#### 2.3.4 Security Mechanisms

Many academic and industrial studies have been conducted on IoT security mechanisms. They focused on detecting various types of attack and intrusion. Security mechanisms typically address one or more elements of the CIA Triad. This included confidentiality, integrity, and availability. The proposed mechanisms may be software- or hardware-based, or software that utilizes hardware acceleration.

In [17], the authors implemented a hardware dynamic information flow tracking (DIFT) architecture for RISC-V processor cores. This DIFT aims to detect memory-corruption attacks, such as buffer overflows and format strings. These mechanisms require modifications at the compiler level. Architectural changes, particularly inside the pipelines, are also necessary. Other countermeasures include memory protection with a safe programming language, such as RUST [47]. The authors of [48] also performed code instrumentation. They added tags to the memory locations for each memory allocation. They used additional tag-checking instructions to find illegal accesses for all memory accesses. Such mechanisms usually require memory layout changes, leading to memory overheads. The tools for static analysis can detect bugs during the compilation stage.

Intrusion and anomaly detection approaches [49,50] have been proposed for IoT environments. They detect attacks using a signature list or by learning the legitimate behavior of a system. This solution comprises three main modules: acquisition, analysis, and alertness. Probes, in hardware or software, collect the system metrics in the acqui-

sition part. This information is then analyzed to identify ongoing attacks. If malicious action is detected, an alert warns the user. These mechanisms are highly accurate in detecting attacks. However, the detection rate performance and overhead, such as area, code size, and power consumption, pose challenges. Lightweight detection algorithms can help resource-constrained IoT devices overcome this overhead. In addition, moving remote analysis and detection algorithms to a server or gateway could be helpful. The end-device then only collects the metrics.

IoT SoC chip manufacturers typically include capabilities, such as cryptographic hardware acceleration for IoT stack protocols. In addition, they include true random number generators, memory encryption, and the ability to perform secure boot and firmware updates. They also have the ability to encrypt data stored in flash memory. These security mechanisms were designed to authenticate the integrity of the firmware. This provides important protection against unauthorized software.

Table 2.5 summarizes the categories of security mechanisms used and unused by the industrial IoT SoC. SoC chip manufacturers for the IoT commonly provide protection and update mechanisms. However, monitoring and detection mechanisms such as intrusion detection systems are usually not included.

Security Mechanisms [10, CC1352R][9, STM32WL55] [11, ESP32-H2] Cryptography X Code Authentification X Protection Secure Boot Memory Encryption 1 Update 🗸 Firmware Update Flow Tracking X X X X X X Detection X Intrusion Detection X X X Anomaly Detection

Table 2.5 – Industrial IoT SoCs Security Features Comparison

Having explored and emphasized security threats associated with wireless connectivity, along with recommended countermeasures, the next section shifts its focus to the field of IDS in this research. Subsequently, we delve into discussions regarding intrusion and anomaly detection approach categories, both established and proposed in research, while also addressing the challenges identified in the process of proposing an IDS solution for IoT devices.

# 2.4 Intrusion Detection System - IDS

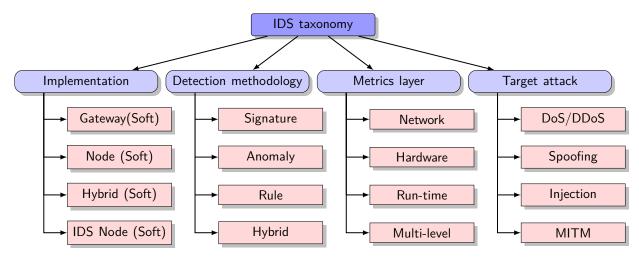

## 2.4.1 IDS Overview and Taxonomy

An IDS is a widely used security mechanism. It monitors and analyzes network or system activities for potential vulnerabilities and attacks. An IDS comprises three main components: acquisition, analysis, and warning. The acquisition component, in the form of hardware or software probes, collects the system information. This can target the network, software, or hardware. The analysis component processes the collected information to identify ongoing attacks. Finally, if there is ongoing malicious activity, the warning component alerts the user.

IDSs often target availability-related attacks, such as DoSs and DDoSs. They can also detect other types of attacks, such as spoofing, packet injection, and MITM attacks.

Implementation and Placement Strategy: An IDS can be placed in an IoT environment such as a smart building as an IoT Node. It can also be embedded in an IoT device or a gateway. Typically, an IDS is implemented as software on these devices. There are two types of IDS: Network-Based Intrusion Detection System (NIDS) and HIDS. An NIDS uses radio probes within an IoT environment to monitor network activities. These activities include the traffic flow and packet headers. Some probes implemented with SDR platforms target multiple frequency bands. In terms of IDS placement, an NIDS is placed in an environment to detect ongoing attacks. An HIDS, on the other hand, can be placed in an IoT device, gateway, or both. It uses embedded probes on each device or gateway to collect and analyze the system data. These data include system calls, memory access, running processes, and MAC and PHY layer features, such as packet headers and RSSI.

## **Detection Methodology:** There are four IDS detection techniques:

- Signature-based: Detects attacks using a matching system or network behavior to compare with an attack signature in the IDS database. An alert is raised if a matching activity is found.

- Anomaly-based: Identifies attacks by comparing legitimate and illegitimate activities. If a deviation over a certain threshold is found, the alert is raised.

- Rule-based: Discovers attacks based on deviations from manually defined specifications and thresholds for normal network component behavior.

— Hybrid-based: Combines signature-based, anomaly-based, and rule-based detection to leverage their advantages and minimize their weaknesses.

**Metrics Layer:** The metrics used by an IDS come from various layers of an IoT Device:

- Network: this includes the protocol stack with different layers (PHY, MAC, and upper layers)

- Hardware: this refers to the processor microarchitecture (pipeline, memory,...)

- Software: this encompasses the run-time or operating system (process, memory,...)

Figure 2.5 provides a summary of IDS taxonomy for an IoT environment. The proposed IDS taxonomy is based on several aspects. These include the placement and detection methodologies, metric layers, and targeted attacks.

Figure 2.5 – IDS Taxonomy for IoT Environment

## 2.4.2 Network-Based IDS

The authors of [51] proposed a DoS detection architecture for IoT devices. This architecture captures and examines network packets using probes specific to a 6LoWPAN network. An IDS detects attacks based on signatures, primarily focusing on flooding attacks. However, the detection rate was relatively low when a single attack probe was used. The detection performance improves when more probes are involved in the same attack.

In [52], the authors leveraged the flexibility of the SDR to target multiple protocols across different ranges. They introduced a demodulation-free Radio-IDS (RIDS) that is

anomaly-based. It uses PHY layer network metrics to detect availability attacks, such as jamming and DoS, as well as integrity attacks, such as MITM, in IoT environments. They constructed a model of legitimate behavior using machine learning, considering factors such as the RSSI and frequency patterns captured from smart home devices using distributed SDR probes.

MedMon, as presented in [53], employs a multilayered anomaly detection system. This system was specifically designed to detect malicious transactions in implantable and wearable medical devices (IWMDs). SDR probes were used to intercept packets and measure the RSSI. Besides these metrics, MedMon incorporates time-series metrics from the MAC and application layers, such as the Time of Arrival (TOA), Differential Time of Arrival (DTOA), and Angle of Arrival (AOA). However, MedMon's focus is strictly on device integrity and does not address availability issues such as jamming attacks.

Table 2.6 provides a comparative analysis of the NIDS discussed in this section. The comparison is structured around several key aspects: the placement strategy, network metrics used, detection methodology, and types of attacks that can be detected.

| NIDS features       | [52]               | [51]     | [53]                  |

|---------------------|--------------------|----------|-----------------------|

| PHY Metrics         | RSSI, Frequency    | X        | RSSI                  |

| MAC Metrics         | X                  | Packet   | X                     |

| Application Metrics | X                  | X        | Transmission schedule |

| Attacks             | DoS, Jamming, MITM | DoS      | Injection             |

| SDR Probes          | $\checkmark$       | ×        | ✓                     |

| Detection           | Behavior           | Behavior | Behavior              |

| Placement           | IDS Device         | Gateway  | IDS Device            |

Table 2.6 – Network-based IDS for IoT

An NIDS with probes is effective for monitoring traffic flow and packet exchange, particularly in small environments such as smart homes. These IDSs can detect ongoing attacks, especially those that affect network availability, based on normal behavior patterns and attack signatures. However, monitoring radio activities alone is insufficient for accurately assessing the IoT security levels. Metrics at the host level, coupled with network metrics, are required to verify intrusions and minimize false positives. An NIDS may struggle to monitor nodes during an attack that compromises a portion of its network. Thus, it is necessary to add more probes to monitor the network activity across the entire environment. However, this leads to significantly increased system costs and

management complexity.

## 2.4.3 Host-Based IDS

An HIDS [50,54,55] incorporates software and/or hardware probes embedded within the system. The HIDS monitors not only network activity but also additional hardware and runtime metrics on IoT devices.

Physical layer IDS (PHY-IDS) [56], an RSSI-based IDS framework, was presented to identify body movement spoofing attacks on wearable devices. First, the system builds a legitimate behavior model using the RSSI time-series data features. This model is then used to spot frames that deviate from the regular wireless signal patterns of legitimate wearable devices. The PHY-IDS can be located in a hub, such as a smartwatch or a smartphone. The experimental results demonstrate that PHY-IDS has an average detection accuracy of approximately 99.8% for naive attacks. However, comprehensive knowledge and advanced learning capabilities are still required to counter the most sophisticated spoofing attacks. Other research works utilized MAC layer metrics, such as packet headers, to detect DoS and jamming attacks. In their work, the authors of [57] proposed Demo, an IDS framework tailored for a 6LoWPAN-supported IoT environment. However, Demo can only be integrated into the gateway and requires additional probes to sniff packets from the IoT devices. [58] is another research that focused on analyzing packet headers to detect spoofing attacks in 6LoWPAN networks. This was achieved using SVELTE, an HIDS integrated with a mini-firewall for IoT devices. SVELTE employs a hybrid detection method based on both signatures and anomalies as well as a hybrid placement strategy. With eight nodes per 6LoWPAN network, SVELTE achieved a high detection rate of approximately 90%. However, as the number of nodes increases, detection accuracy is affected. For example, with 32 nodes, the detection rate dropped to 70%.

The authors of [50] utilized metrics from both the MAC and physical layers. For example, Passban IDS uses anomaly-based detection with RSSI and packet headers to identify malicious packet injections in Linux-based IoT gateway devices. It is capable of detecting various types of malicious traffic, such as port scanning, HTTP and SSH brute-force attacks, and SYN flooding. However, the assessment of Passban IDS has a considerable impact on the IoT gateway: it incurs a 6% memory overhead, increases CPU usage by 30%, and reduces network speed by 7%. This suggests that it is unsuitable for embedding in smaller devices. Certain hardware metrics can be utilized to implement an

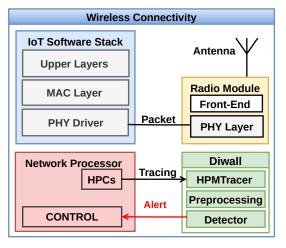

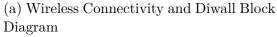

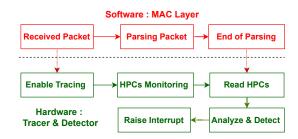

HIDS that can detect attacks, particularly those that compromise integrity.